# **Sequential Logic Synthesis**

This presentation can be used for non-commercial purposes as long as this note and the copyright footers are not removed

© Giovanni De Micheli – All rights reserved

**Delft University of Technology**

- Objective

- Structural representation of sequential circuits

- Retiming

- •

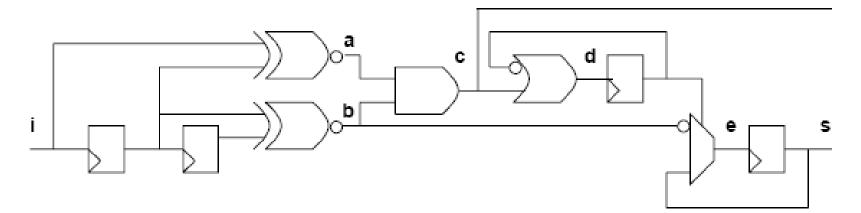

## **Structural model for sequential circuits**

- Synchronous logic network

- Variables

- Boolean equations

- Synchronous delay annotation

- Synchronous network graph

- Vertices ↔ equations ↔ I/O, gates

- Edges ↔ dependencies ↔ nets

- Weights ↔ synchronous delays ↔ registers

**T**UDelft

#### **Approaches to sequential synthesis**

- Optimize combinational logic only

- Freeze circuit at register boundary

- Modify equation and network graph topology

- Retiming

- Move register positions. Change weights on graph

- Preserve network topology

- Synchronous transformations

- Blend combinational transformations and retiming

- Powerful, but complex to use

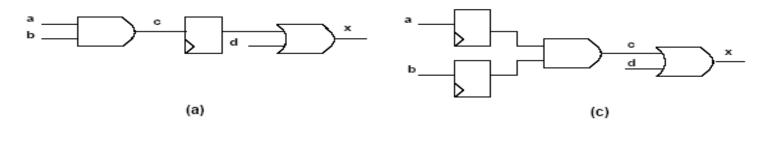

#### **Example of local retiming**

(b)

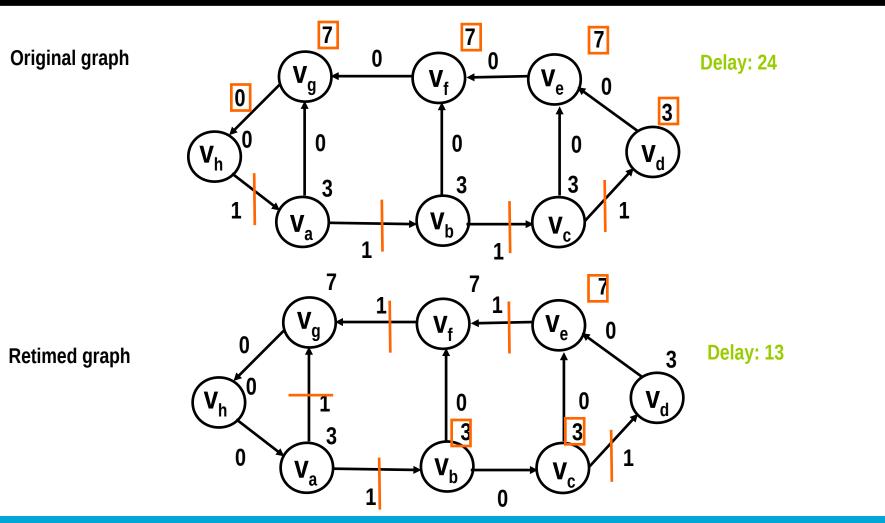

- Global optimization technique

- Change register positions

- Affects area:

- Retiming changes register count

- Affects cycle-time

- Changes path delays between register pairs

- Retiming algorithms have polynomial-time complexity

## **Retiming assumptions**

- Delay is constant at each vertex

- No fanout delay dependency

- Graph topology is invariant

- No logic transformations

- Synchronous implementation

- Cycles have positive weights

- Each feedback loop has to be broken by at least one register

- Edges have non-negative weights

- Physical registers cannot anticipate time

- Consider topological paths

- No false path analysis

#### Retiming

•

- Retiming of a vertex v

- Integer r<sub>v</sub>

- Registers moved from output to input  $r_v$  positive

- Registers moved from input to output  $r_v$  negative

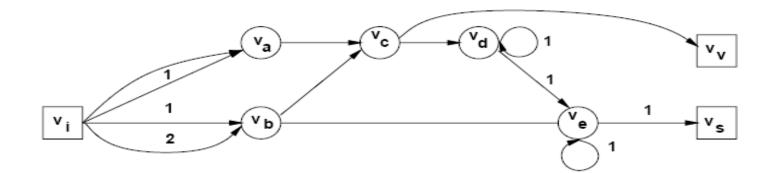

#### Example 9.3.4

## **Definitions and properties**

- Definitions:

- $(v_i, ..., v_j)$  path from  $v_i$  to  $v_j$

- w( $v_i$ , ...,  $v_j$ ) weight on path from  $v_i$  to  $v_j$

- d( $v_i$ , ...,  $v_j$ ) combinational delay on path from  $v_i$  to  $v_j$

- Properties:

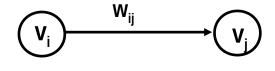

- Retiming of an edge ( $v_i$ ,  $v_j$ )

- $\hat{\mathbf{w}}_{ij} = \mathbf{w}_{ij} + \mathbf{r}_j \mathbf{r}_i$

- Retiming of a path ( $v_i$ , ...,  $v_j$ )

- $\hat{w}(v_i, ..., v_j) = w(v_i, ..., v_j) + r_j r_i$

• Cycle weights are invariant

## Legal retiming

- Clock period φ

- A retiming vector is legal if:

- No edge weight is negative

- $\hat{w}_{ij} (v_i, v_j) = w_{ij} (v_i, v_j) + r_j r_i \ge 0$  for all i, j

- Each path ( $v_i$ , ...,  $v_j$ ) with d ( $v_i$ , ...,  $v_j$ ) >  $\phi$  has at least one register:

- $\hat{w}(v_i, ..., v_j) = w(v_i, ..., v_j) + r_j r_i \ge 1$  for all i, j

- Equivalently, each combinational path delay is less than  $\boldsymbol{\phi}$

## **Refined analysis**

- Least-register path

- W (v<sub>i</sub>, v<sub>j</sub>) = min w (v<sub>i</sub>, ..., v<sub>j</sub>) over all paths between v<sub>i</sub> and v<sub>j</sub>

- Critical delay:

- D (v<sub>i</sub>, v<sub>j</sub>) = max d (v<sub>i</sub>, ..., v<sub>j</sub>) over all paths between v<sub>i</sub> and v<sub>j</sub> with weight W (v<sub>i</sub>, v<sub>j</sub>)

- There exist a vertex pair  $(v_i, v_j)$  whose delay D  $(v_i, v_j)$  bounds the cycle time

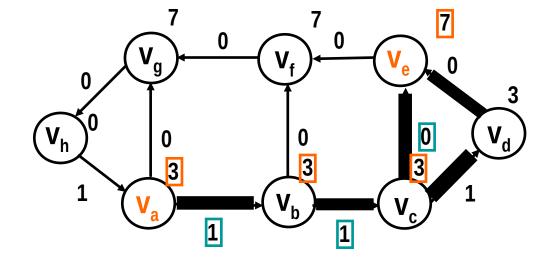

#### Example 9.3.9

•Vertices: V<sub>a</sub>, V<sub>e</sub>

- •Paths:  $(v_a, v_b, v_c, v_e)$  and  $(v_a, v_b, v_c, v_d, v_e)$

- •W(v<sub>a</sub>, v<sub>e</sub>) = 2 •D(v<sub>a</sub>, v<sub>e</sub>) = 16

Maximum delay on path with minimum register count

## **Other problems related to retiming**

- Retiming pipelined circuits

- Balance pipe stages by using retiming

- Trade-off latency versus cycle time

- Peripheral retiming

- Use retiming to move registers to periphery of a circuit

- Restore registers after optimizing combinational logic

- Wire pipelining

- Use retiming to pipeline interconnection wires

- Model sequential and combinational macros

- Consider wire delay and buffering

## **Summary of retiming**

- Sequential optimization technique for:

- Cycle time or register area

- Applicable to

- Synchronous logic networks

- Architectural models of data paths

- Vertices represent complex (arithmetic) operators

- Exact algorithm in polynomial time

- Extension and issues

- Delay modeling

- Network granularity