# VLSI Test Technology and Reliability (ET4076)

Lecture 8(2)

# IDDQ Current Testing (Chapter 13)

Said Hamdioui

Computer Engineering Lab Delft University of Technology 2009-2010

## Learning aims

- Describe the concept of current testing IDDQ & its added value

- Describe the major faults and defects that can be detected by IDDQ

- Develop a vector for IDDQ

- State the major limitations of IDDQ and remedies

## Contents

- Motivation

- IDDQ Test Concept

- Pros and cons

- Coverage

- Vector generation for *IDDQ* tests

- Instrumentation difficulties

- IDDQ testing effectiveness

- Limitations of *IDDQ* testing

- Delta IDDQ testing

- Built-in Current testing

- Summary

# **Motivation**

- Early 1990's Fabrication Line had 50 to 1000 defects per million (dpm) chips

- IBM wants to get 3.4 *defects per million* (dpm) chips (0 defects, 6 σ)

Conventional way to reduce defects:

- Increasing test fault coverage

- Increasing burn-in coverage

- Increase Electrostatic Discharge Damage awareness

#### New way to reduce defects:

IDDQ Testing also useful for Failure Analysis

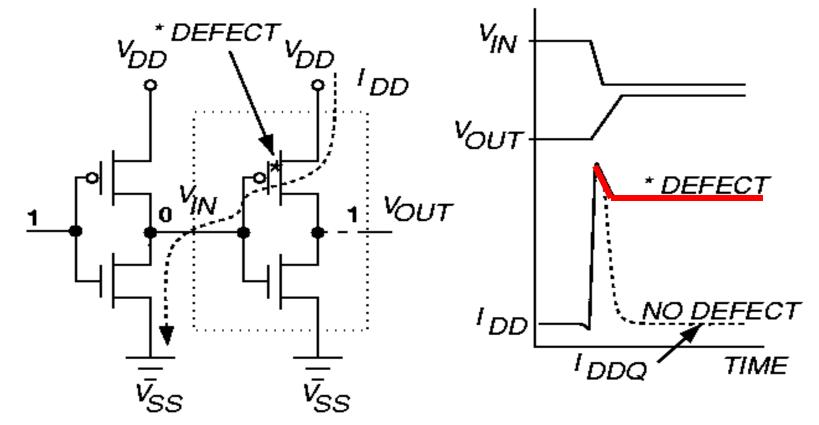

# I<sub>DDQ</sub> Test Concept

In a good circuit, IDDQ (Quiescent current) is negligible

- In a faulty circuit, IDDQ remain elevated after switching

- Measure  $I_{DDO}$  current through  $V_{ss}$  bus to detect the fault

- Can also measured through the VDD bus

- ATE or "current measurement device" can perform measurements

VLSI Test Technology and Reliability, 2009-2010

CE Lab, TUDelft

# *I*<sub>DDQ</sub> Test ..... + and -

- □ *I<sub>DDQ</sub>* **measure** current: slow

- I IDDQ was used functional test, delay test, memory test, ...

- Used to improve the IC reliability, reduce manufacturing cost by 50%, improve filed quality, cut burn-in failures

### Problems

- Feature size in the nano-era

- Increase in leakage

# *I<sub>DDQ</sub>* Test coverage (1)

### IDDQ can detect many faults and defects:

- Stuck at faults

- Delay faults

- Weak faults

- Bridging faults

- CMOS Stuck-Open faults

- Leakage current

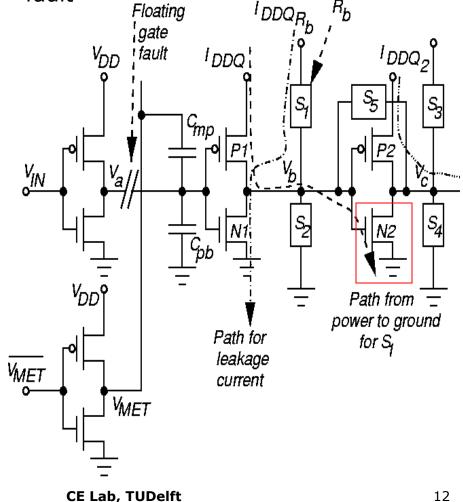

- Floating gate defects

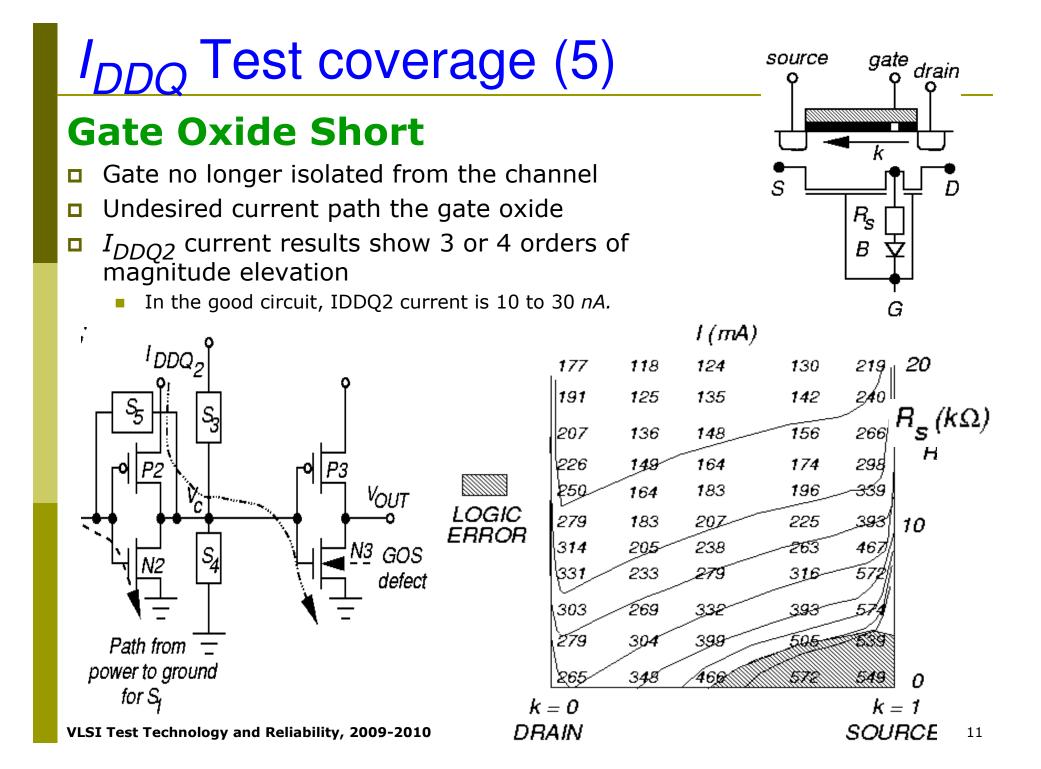

- Gate Oxide Shorts

- etc

# *I<sub>DDQ</sub>* Test coverage (2)

### Stuck at faults

- Defects causing n and pFET transistors in a gate to be **on**

- Bridging faults with stuck-at fault behavior

#### Delay faults

- Most random CMOS defects cause a timing delay fault, not catastrophic failure

- Many delay faults detected by I<sub>DDQ</sub> test late switching of logic gates keeps I<sub>DDQ</sub> elevated

- Delay faults not detected by  $I_{DDO}$  test

- Resistive via fault in interconnect

- Increased transistor threshold voltage fault

# I<sub>DDQ</sub> Test coverage (3)

### Weak faults

- *n*FET passes logic 1 as Vdd V<sub>tn</sub>

- *p*FET passes logic 0 as 0 V +  $|V_{tp}|$

- Weak fault: transistor not fully turn on, so the signal passed is degraded

- Increased propagation delay

- Increases noises

### CMOS Stuck-Open faults

- 100% detection not guaranteed

- But work good in practice

Intermediate voltage of floating gate, hence high IDDQ

#### $I_{DDO}$ Test coverage (4) **Floating gate defects NAND** Gate V<sub>fn</sub> voltage depends on the defect size Small defect (100 – 200 Angstroms) V<sub>DD</sub> Coupling between the two wires Delay fault Weak voltage at the defective node PA Detected with IDDQ $V_A$ דו ור Large open Floating gate Stuck at fault? Sometime can be detected • If $V_{tn} < V_{fn} < V_{DD} - |V_{tp}|$ Interconnect Break

# Vector generation for $I_{DDQ}$ tests (1)

#### **Leakage Fault Detection**

[Mao and Gulati]

- Sensitize leakage fault

- Detection 2 transistor

terminals with leakage must

have opposite logic values, & be

at driving strengths

- Non-driving, high-impedance states won't work – current cannot go through them

- N2 with gate-source leakage

- Detection requires Vb=1 and VIN=1

- This create the leakage through the fault

# Vector generation for $I_{DDQ}$ tests (2)

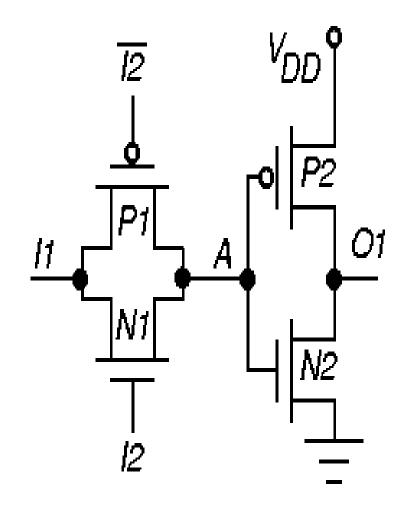

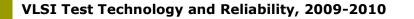

### Weak Fault Detection – P1 (N1) Open

- P1(N1) degrades the input voltage

- Both transistors of inverter remain partially turned on

- Elevating I<sub>DDQ</sub> from 0 μA to 56 μA

# Vector generation for $I_{DDQ}$ tests (3)

### Weak Fault Detection – P1 Open

- P1 degrades the input voltage

- IDDQ will be not elevated unless I3 is set to 1

- No IDDQ path can exist if I3=0

# Vector generation for $I_{DDQ}$ tests (4)

### **Hierarchical Vector Selection**

- Generate complete stuck-fault tests

- Characterize each logic component relate input/output logic values & internal states:

- To leakage fault detection

- To weak fault sensitization/propagation

- Uses <u>switch-level</u> simulation (once for each component)

- Store information in *leakage* & weak fault tables

- Logic simulate stuck-fault tests use tables to find faults detected by each vector

- No more switch-level simulation

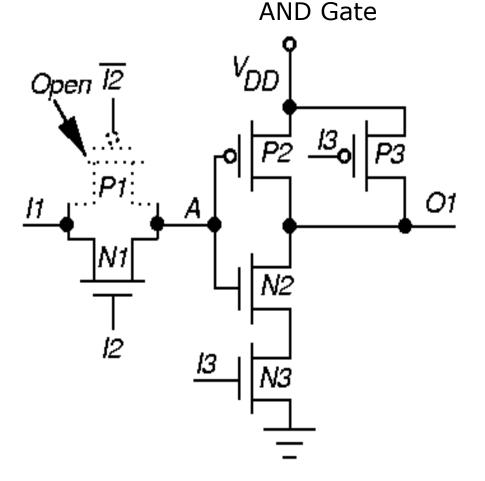

# Vector generation for $I_{DDQ}$ tests (5)

### Leakage Fault Table

- $\square k = #$  component I/O pins

- n = # component transistors

- $\square m = 2^k$  (# of input / output combinations)

- □ *m* x *n* matrix *M* represents the table

- Each logic state 1 matrix row

- **D** Entry  $m_{i i} = \text{octal}$  leakage fault information

- 6 Flags  $f_{BG} f_{BD} f_{BS} f_{SD} f_{GD} f_{GS}$

- Sub-entry m<sub>ij</sub> = 1 if leakage fault detected

## Vector generation for $I_{DDQ}$ tests (6)

#### Leakage Fault Table: Example

# Instrumentation difficulties

Need to measure < 1 µA current at clock > 10 kHz

□ Off-chip *I*<sub>DDQ</sub> measurements degraded

- Pulse width of CMOS IC transient current

- Impedance loading of tester probe

- Current leakages in tester

- High noise of tester load board

Much slower rate of current measurement than voltage measurement

## IDDQ testing effectiveness

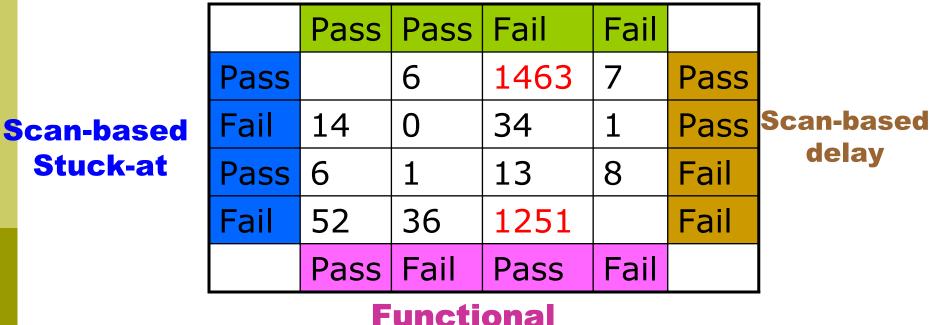

- HP static CMOS standard cell design (8577 gates and 436FFs)

- There is less correlation between IDDQ failures and voltage failures in general

- A mixture of testing methods is required to achieve a high product reliability

- IDDQ improve reliability

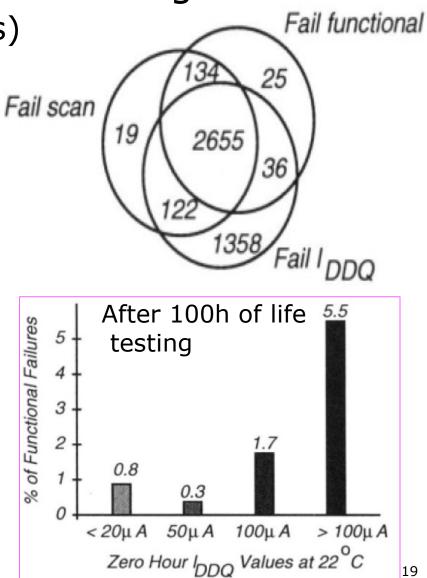

### IDDQ testing effectiveness... Sematech Study(1)

- IBM Graphics controller chip CMOS ASIC, 166,000 standard cells

- 0.8 μm static CMOS, 0.45 μm Transistors (L<sub>eff</sub>), 40 to 50 MHz Clock, 3 metal layers, 2 clocks

- Full boundary scan on chip

#### Tests:

- Scan-based stuck-at faults (99.7% FC, slow 400ns rate)

- Functional tests (design verification patterns;52% SAF FC; manually created)

- Scan based delay fault test (90 % transition delay FC)

- *I<sub>DDQ</sub>* Tests (125) (96 % pseudo-stuck-at fault coverage).

### IDDQ testing effectiveness... Sematech Study(2)

- □ Test process: Wafer Test → Package Test → Burn-In & Retest → Characterize & Failure Analysis

- Data for devices failing some, but not all, tests.

#### *IDDQ* (5 µA limit)

All test methods uniquely detected some defect class

=> none can be dropped from the test program

### IDDQ testing effectiveness... Sematech Study(3)

### **Sematech Conclusions:**

- Hard to find point differentiating good and bad devices for  $I_{DDQ}$  & delay tests

- High # passed functional test, failed all others

- **\square** High # passed all tests, failed  $I_{DDO} > 5 \mu A$

- Large # passed stuck-at and functional tests

- Failed delay & IDDQ tests

- Large # failed stuck-at & delay tests

- Passed I<sub>DDQ</sub> & functional tests

- Delay test caught delays in chips at higher temperature burn-in

- chips passed at lower temperature

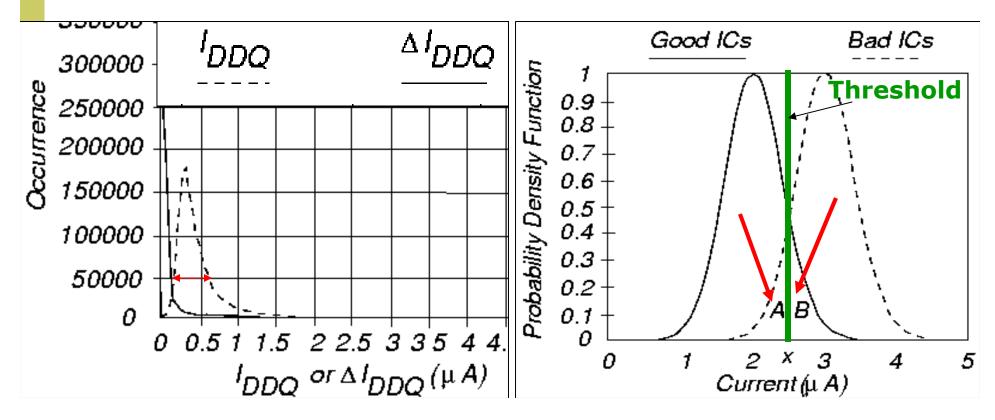

## Limitations of *I<sub>DDQ</sub>* Testing

- Sub-micron technologies have increased leakage currents

- Transistor sub-threshold conduction

- Harder to find I<sub>DDO</sub> threshold separating good & bad chips

- $I_{DDQ}$  tests work:

- 1. When average defect-induced current greater than average good IC current

- 2. Small variation in  $I_{DDQ}$  over test sequence & between chips

- Detect passive defects and active defects simultaneously

- Now less likely to obtain two conditions (scaling)

- Some predict the end of IDDQ testing

## Delta I<sub>DDQ</sub> Testing..... [Thibeault]

- Use derivative of I<sub>DDQ</sub> at test vector as current signature

- $\Delta I_{DDQ}(i) = I_{DDQ}(i) I_{DDQ}(i-1)$

- Leads to a narrower histogram

- Eliminates any variation between chips (wafers)

## Delta I<sub>DDQ</sub> Testing..... Results

### $\Box \Delta I_{DDQ}$ Testing versus $I_{DDQ}$ testing Results

- P: probability of a false decision

- AI<sub>DDQ</sub> eliminates any constant (vector-insensitive) current increase due to process drift by differential operation

- But process drift may still increases the measurement variations between vectors

| Item                    | <b>I</b> <sub>DDQ</sub> | $\Delta \mathbf{I}_{DDQ}$ |

|-------------------------|-------------------------|---------------------------|

| RYL (yield loss ratio)  | 4.4e-4                  | 3.5e-3                    |

| RTE (test escape ratio) | 1.8e-1                  | 2.1e-3                    |

| P (= RYL + RTE)         | Piddq = 1.8e-1          | <i>Pdelta</i> = 5.6e-3    |

| Gain in test quality    | Piddq / Pdelta = 31     |                           |

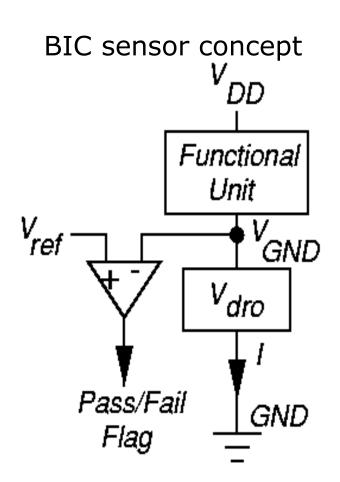

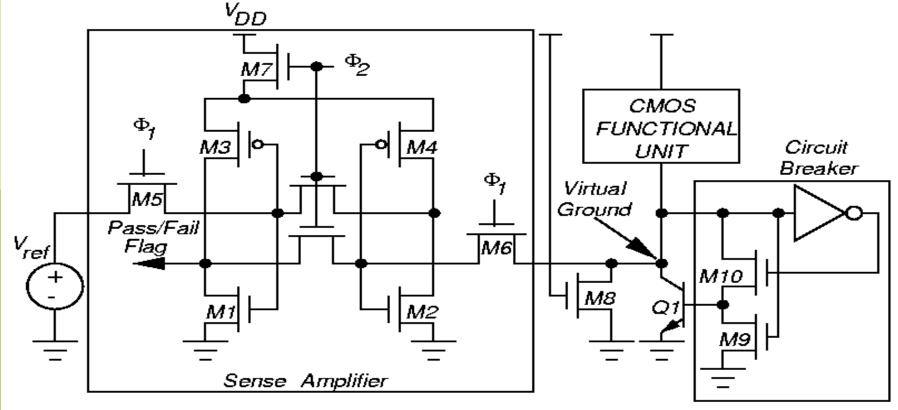

Built-in Current Testing.... [Maly and Nigh]

- Build current sensor into ground bus of device-under-test

- Voltage drop device (V<sub>dro</sub>)& comparator

- Compares virtual ground

V<sub>GND</sub> with V<sub>ref</sub> at end of each clock

- V<sub>GND</sub> > V<sub>ref</sub> only in bad circuits

- Activates circuit breaker when bad device found

## Built-in Current Testing.... Example

- A bipolar transistor is used to get better resolution for current detection

- Circuit Breaker disconnect the defective functional unit from power when abnormal currents occur (e.g., due to VDD-GND shorts)

# Summary

$\Box$   $I_{DDO}$  tests improve reliability, find defects causing:

- Delay, bridging, weak faults

- Chips damaged by electro-static discharge

- No natural breakpoint for current threshold

- Get continuous distribution bimodal would be better

- Conclusion: now need stuck-fault, I<sub>DDQ</sub>, and delay fault testing combined

- $\Box$   $I_{DDO}$  testing is becoming more problematic

- Greater leakage currents in MOSFETs in deep sub-micron technologies

- Harder to discriminate elevated I<sub>DDQ</sub> from 100,000 transistor leakage currents

- $\Box \Delta I_{DDQ}$  holds promise to alleviate problems

- Built-in current testing holds promise