# VLSI Test Technology and Reliability (ET4076)

Lecture 7

# **Memory Testing**

Said Hamdioui

Computer Engineering Lab Delft University of Technology 2009-2010

Faculty: Section: Date: Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Engineering Laboratory (CE) 2009-2010

# **Motivation**

- Combinational logic contains no flip flops (no memory)

- Space of possible tests is

- O(2<sup>no\_pi</sup>), no\_pi = #primary inputs

- If no\_pi = 64 & circuit runs @ 1GHz How long does a full test take??

→ full test takes 585 years!

- How can we deal with this problem??

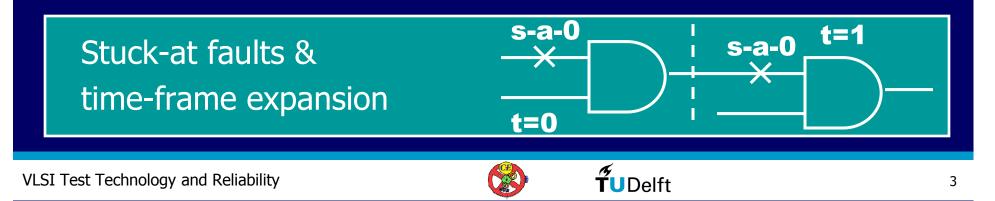

Stuck-at faults are used to model defects and limit test space

# **Motivation**

- Sequential logic contains some flip flops (limited memory)

- Space of possible tests is

- O(2<sup>no\_pi</sup> x 2<sup>no\_ff</sup>)

no\_pi = #primary inputs

no\_ff = #flip flops

- If no\_pi = 64, no\_ff = 16 @ 1GHz How long should we test??

test takes about 50 million years!

- How can we deal with this problem??

# **Motivation**

- Memory contains millions of states

- Testing memory is EXTREMELY difficult

- Exhaustive testing takes more than the age of the UNIVERSE!!

• Special fault models are needed

### Learning aims

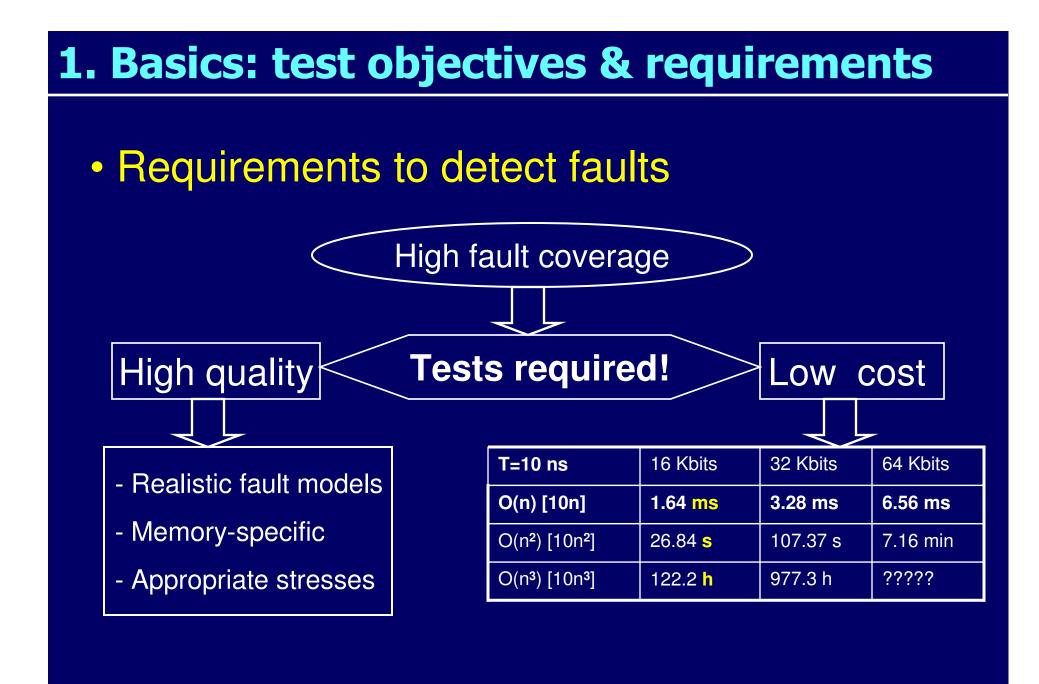

- Describe the problem of memory testing, its objectives and its importance

- Describe different fault types

- Define the different memory fault models

- Classify the memory test algorithms

- Analyze the fault coverage of memory algorithms

- Develop memory algorithms for given fault models

- Describe the major challenges for memory testing

# Contents

- 1. Basics of memory devices

- 2. Semiconductor memory architecture

- 3. Functional fault models

- 4. Memory test development

- (to detect the memory faults we defined)

- 5. Well-known memory tests

# VLSI Test Technology and Reliability (ET4076)

### Memory Testing: 1. Basics of memory devices

Faculty: Section: Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Engineering Laboratory (CE)

# **1.** Basics of memory devices

# **Topics:**

- History of memory

- History of DRAM

- History of SRAM

- Importance of memory testing

- Test objectives and requirements

# **1.** Basics: history of memory

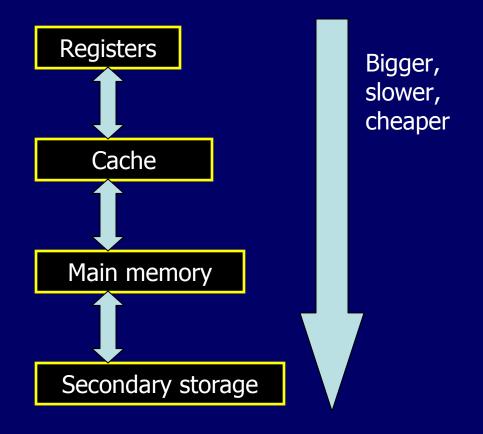

- Memory is important for data processing

- More memory needed for faster CPUs

- Hierarchy of memory used:

- Registers: Flip flops

- Cache: SRAM

- Main: DRAM

- Secondary: Hard disk

# **1. Basics: history of DRAM**

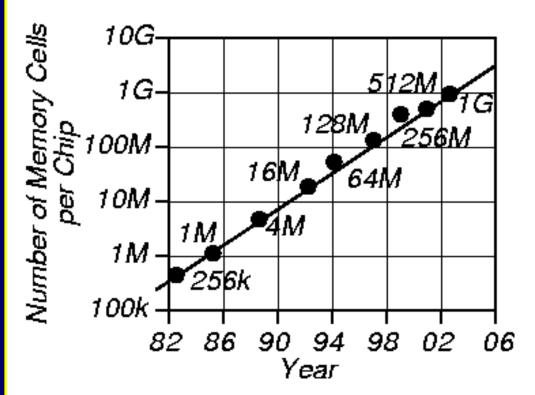

#### DRAMs are

- Widely used

- Standalone chip

- Most sensitive VLSI chip

- Increase exponentially in size

- 32 GB+ in 2020!

# **1.** Basics: history of SRAM

#### SRAMs are

- Widely used ullet

- **Embedded with logic** ightarrow

- More sensitive than  $\bullet$ logic

- Increase in size ullet

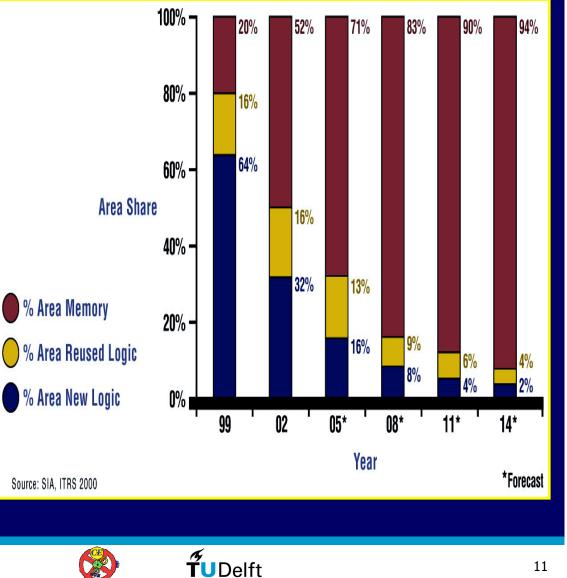

- Dominate chip area ightarrow

- 94% in 2014!

# **1. Basics: importance of memory testing**

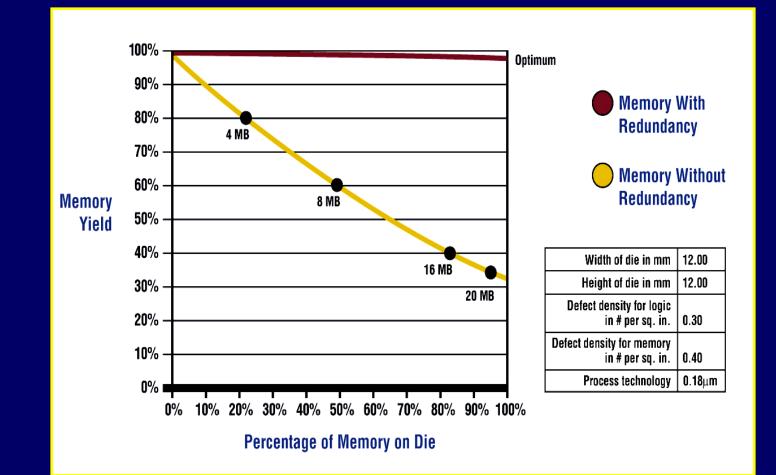

Yield decreases dramatically with increasing in memory size

Redundancy dramatically improves memory yield

# VLSI Test Technology and Reliability (ET4076)

### Memory Testing: 2. Semiconductor memory architecture

Faculty: Section: Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Engineering Laboratory (CE)

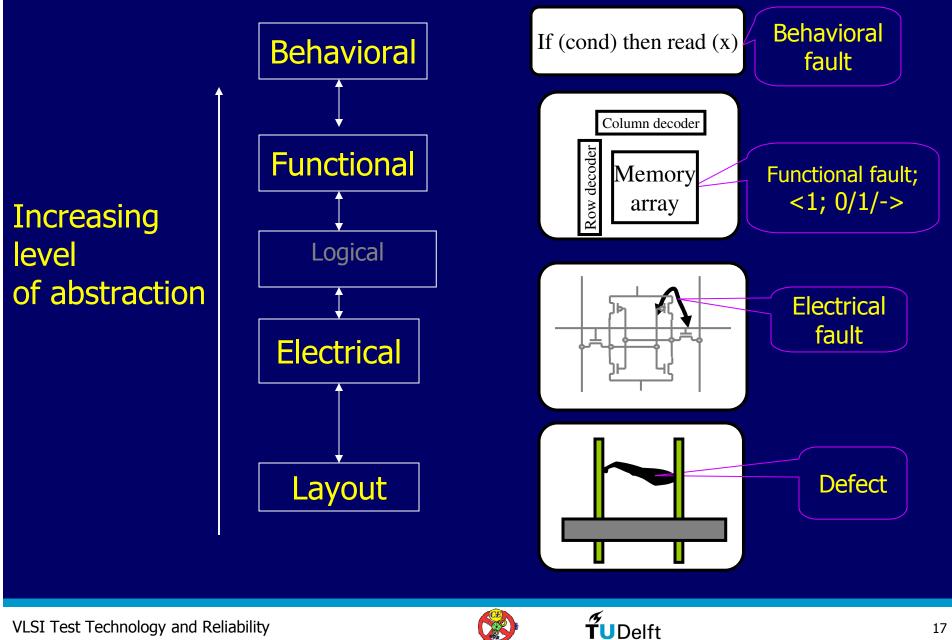

# **2. Semiconductor memory architecture**

# **Topics:**

- Memory models

- Behavioral model

- Functional model

- Electrical model

- Layout model (rarely reported)

# **2. Architecture: memory models**

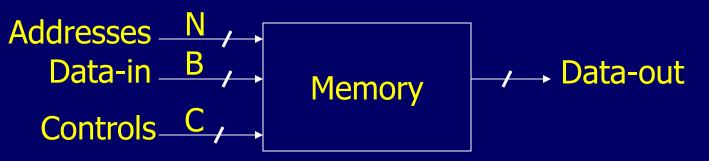

# **2. Architecture: behavioral model**

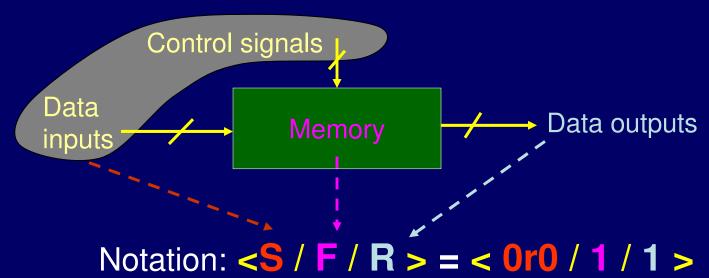

- General memory Model

- Nothing known about the internal structure

- Data sheet describing functionality provided

- B: the word width

- Data-in and Data-out are usually combined

=> Bi-directional data lines

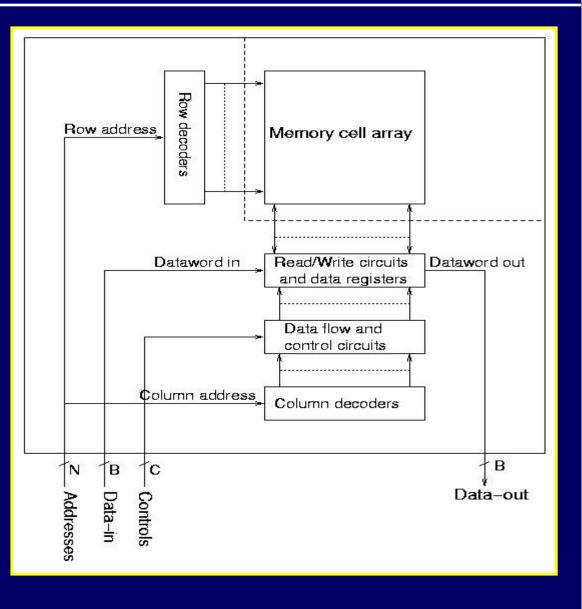

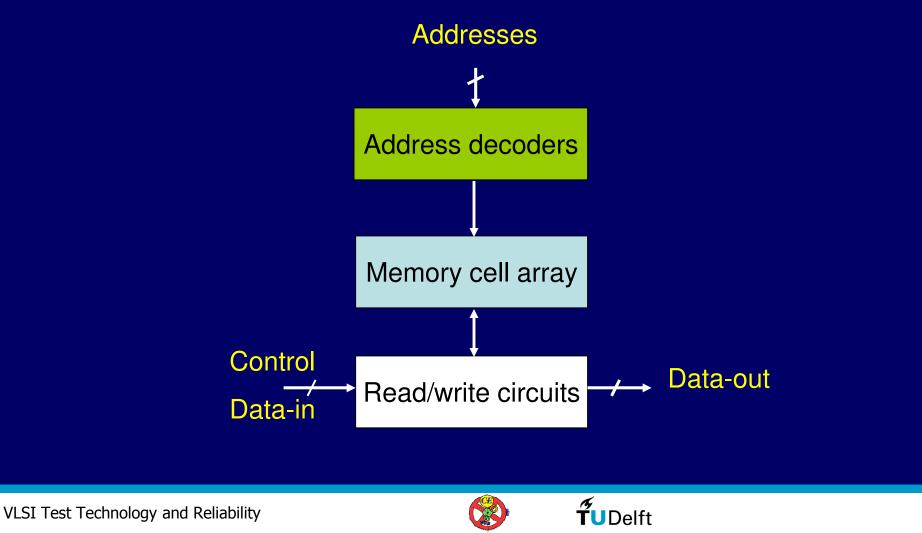

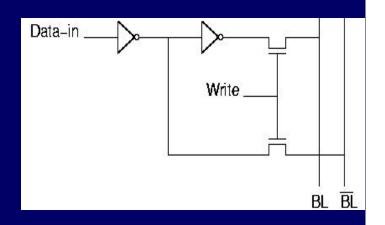

# **2. Architecture: functional model**

- Functions of the system

- functional blocks (with behavior model)

- Memory cell array consist of *n* cells *n = R x C R*: Rows (Word lines) *C*: Columns (Bit lines)

**T**UDelft

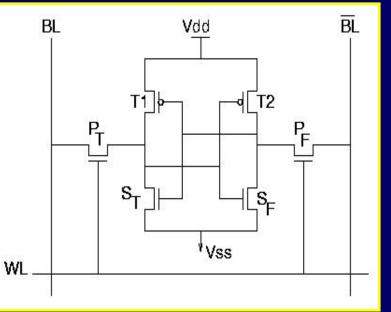

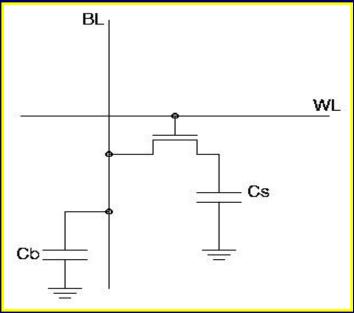

# 2. Architecture: electrical model (array)

#### SRAM cell (CMOS)

Six Transistors per bit Low density Fast access time (e.g., 2ns) High prices DRAM cell (1T)

Due to leakage, refresh required High density Low access time (e.g., 20 ns) Low prices

VLSI Test Technology and Reliability

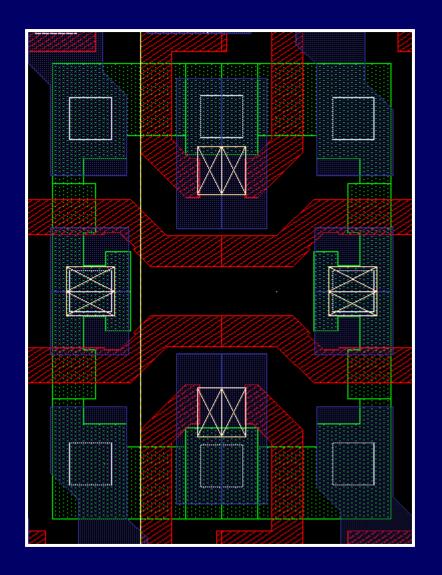

# 2. Architecture: layout model (array)

- Physical implementation of the system

- Diffusion regions, metal layers, contacts, etc.

- Most detailed description of any system

- Most complex level to analyze

- Usually confidential

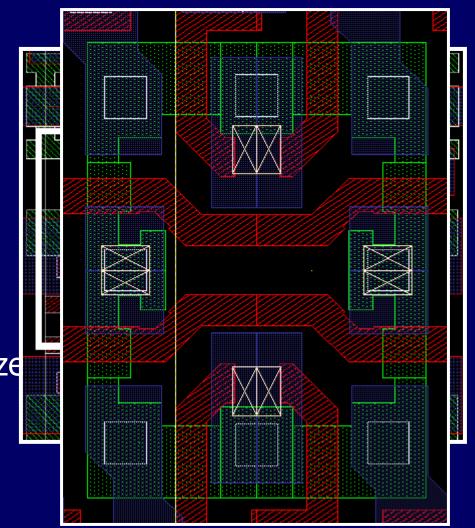

# 2. Architecture: layout model (array)

- Physical implementation of the system

- Diffusion regions, metal layers, contacts, etc.

- Most detailed description of any system

- Most complex level to analyze

- Usually confidential

# VLSI Test Technology and Reliability (ET4076)

### Memory Testing: 3. Functional fault models

Faculty: Section: Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Engineering Laboratory (CE)

# 3. Functional fault models

# **Topics:**

- Reduced memory model

- Memory cell array faults

- Fault primitive concept

- Classification

- Definition of fault models

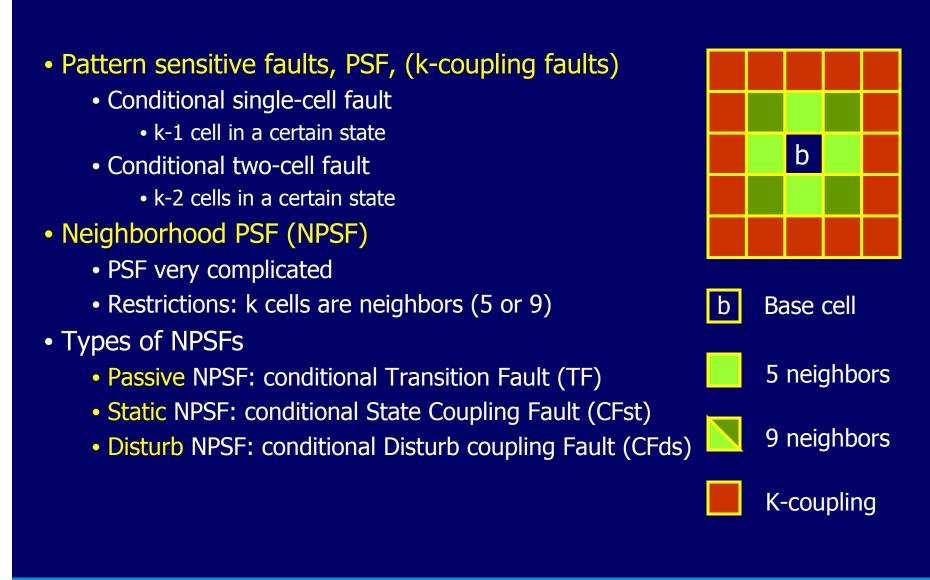

- Neighborhood pattern sensitive faults

- Address decoder faults

- Read/Write logic faults

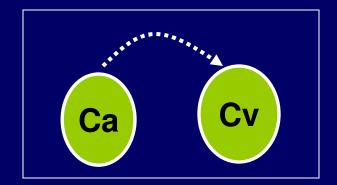

# 3. Faults: reduced memory model

• Memory faults can be divided into three types/classes

# 3. Faults: array (fault primitives and fault models)

#### Fault primitive concept (FP)

- S: sensitizing sequence; e.g. a read 0 operation (0r0)

- F: Fault effect; e.g. cell flips from 0 to 1 (1)

- R: Read value; e.g. an incorrect value 1 is read (1)

- A Fault model (FM) is a non-empty set of FPs

- E.g., Read Destructive Fault (RDF): {<0r0/ 1 / 1 >, <1r1/ 0 / 0 >}

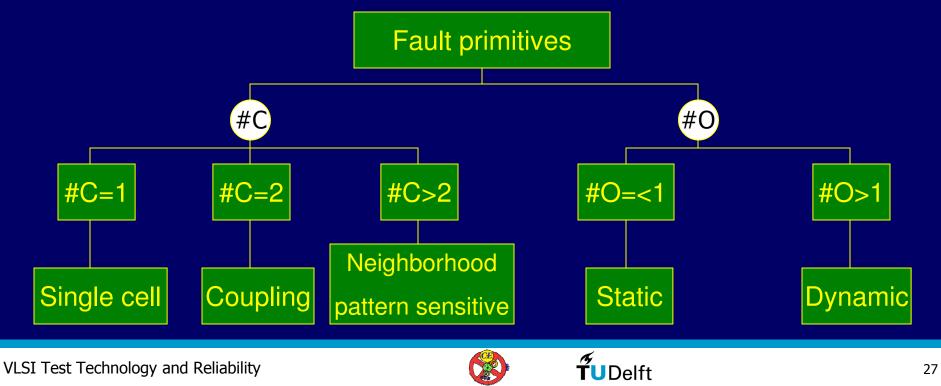

### 3. Faults: array (classification of fault primitives)

#### Fault Primitive: FP = <S/F/R>

- Depending on #Cells (C) in S

- Single-cell, two-cell, and neighborhood pattern sensitive faults

- Depending on #Operations (O) in S

- Static faults versus dynamic faults

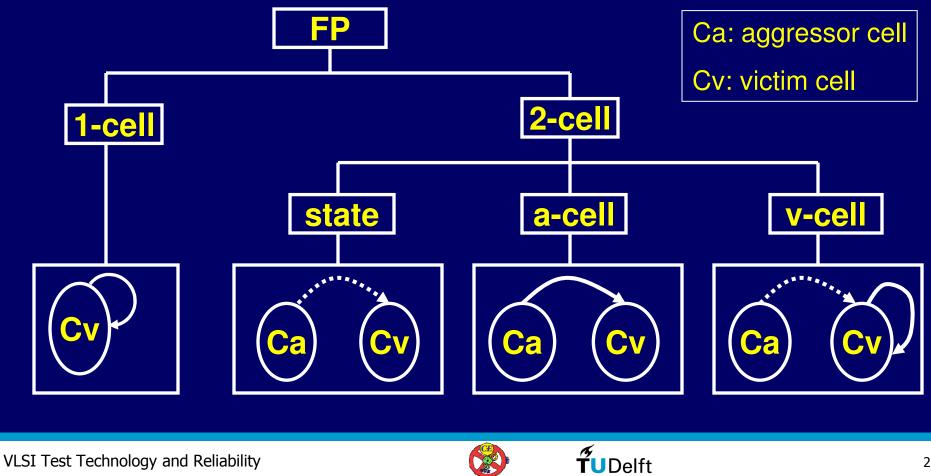

### 3. Faults: array (classification of fault primitives)

- Static faults can be classified as: ightarrow

- Single-cell (1-cell)

- Two-cells (2-cell) (i.e., coupling faults)

• Single-cell FPs: <S/F/R>Se {0,1,0w0,1w1,0w1,1w0, 0r0, 1r1} Fe {0,1} Re {0,1,-}

Compile the 12 FPs into 6 FMs

1. State Fault {1,2} (SF)/(SAF)

2. Write Disturb Fault {3,4} (WDF)

3. Transition Fault {5,6} (TF)

4. Incorrect Read Fault {7, 10} (IRF)

5. Read Destructive Fault {9, 12} (RDF)

6. Deceptive Read Destructive Fault {8,11} (DRDF)

| #  | S   | F | R | <s f="" r=""></s>     |

|----|-----|---|---|-----------------------|

| 1  | 0   | 1 | _ | <0/1/->               |

| 2  | 1   | 0 | - | <1/0/->               |

| 3  | 0w0 | 1 | - | <0w0/1/->             |

| 4  | 1w1 | 0 | - | <1w1/0/->             |

| 5  | 0w1 | 0 | - | <0w1/0/->             |

| 6  | 1w0 | 1 | - | <1w0/1/->             |

| 7  | 0r0 | 0 | 1 | <0r0/0/1>             |

| 8  | 0r0 | 1 | 0 | <r0r 0="" 1=""></r0r> |

| 9  | 0r0 | 1 | 1 | <0r0/1/1>             |

| 10 | 1r1 | 1 | 0 | <1r1/1/0>             |

| 11 | 1r1 | 0 | 1 | <1r1/0/1>             |

| 12 | 1r1 | 0 | 0 | <1r1/0/0>             |

• Two-cell FPs: state

<S/F/R> = <Sa; Sv/F/R>Sa  $\in \{0,1\}, Sv \in \{0,1\}$ F  $\in \{0,1\}$ R  $\in \{0,1,-\}$

### Compile the 4 FPs into 1 FM: State Coupling Fault (CFst)

| # | Sa | Sv | F | R | <sa; f="" r="" sv=""></sa;> |

|---|----|----|---|---|-----------------------------|

| 1 | 0  | 0  | 1 | _ | <0; 0/1/->                  |

| 2 | 0  | 1  | 0 | - | <0; 1/0/->                  |

| 3 | 1  | 0  | 1 | - | <1; 0/1/->                  |

| 4 | 1  | 1  | 0 | _ | <1; 1/0/->                  |

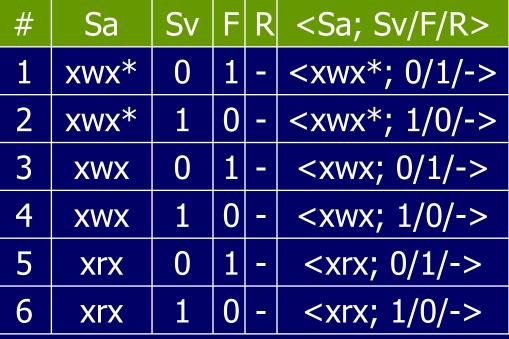

Two-cell FPs: a-cell accessed  $Sa \in \{0w0, 1w1, 0w1, 1w0, 0r0, 1r1\}$   $Sv \in \{0,1\}; F \in \{0,1\}; R \in \{-\}$   $x^* = NOT x; x \in \{0,1\}$ r = read; w = write# Sa

#### Compile the 12 FPs into 1 FM: Disturb Coupling Fault (CFds)

CFds divided into 3 types:

- CFds<sub>t</sub> {1, 2} (transition write)

- CFds<sub>n</sub> {3, 4} (non-trans. write)

- CFds<sub>r</sub> {5,6} (read)

#### Two-cell FPs: 1PF2v (v-cell accessed)

Sa  $\in$  {0,1} Sv  $\in$  {0w0,1w1,0w1,1w0, 0r0, 1r1} F  $\in$  {0,1} R  $\in$  {0,1,-} x  $\in$  {0,1}

### Compile the 24 FPs into 5 FMs:

- CF= Coupling Fault

- 1. Write Disturb CF {1,2} (CFwd)

- 2. Transition CF {3,4} (CFtr)

- 3. Incorrect Read CF {5,8 } (CFir)

- 4. Read Destructive CF {7,10}(CFrd)

- 5. Deceptive CFrd {6,9} (CFdr)

| #  | Sa | Sv         | F | R | <s f="" r=""></s>          |

|----|----|------------|---|---|----------------------------|

| 1  | X  | 0w0        | 1 | - | <x; -="" 0w0="" 1=""></x;> |

| 2  | Х  | 1w1        | 0 | - | <x; -="" 0="" 1w1=""></x;> |

| 3  | X  | 0w1        | 0 | - | <x; -="" 0="" 0w1=""></x;> |

| 4  | X  | 1w0        | 1 | - | <x; -="" 1="" 1w0=""></x;> |

| 5  | X  | 0r0        | 0 | 1 | <x; 0="" 0r0="" 1=""></x;> |

| 6  | X  | 0r0        | 1 | 0 | <x; 0="" 1="" r0r=""></x;> |

| 7  | X  | <b>0r0</b> | 1 | 1 | <x; 0r0="" 1=""></x;>      |

| 8  | X  | 1r1        | 1 | 0 | <x; 0="" 1="" 1r1=""></x;> |

| 9  | X  | 1r1        | 0 | 1 | <x; 0="" 1="" 1r1=""></x;> |

| 10 | X  | 1r1        | 0 | 0 | <x; 0="" 1r1=""></x;>      |

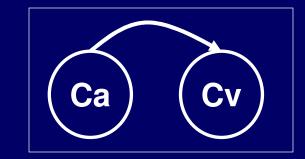

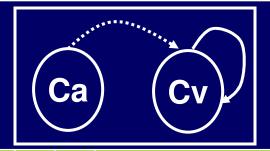

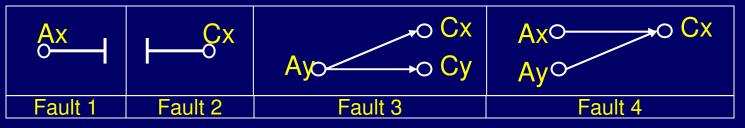

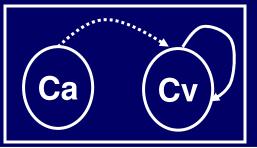

# 3. Faults: address decoder (functional faults)

- 1-1 correspondence: Address <----> Cell

- Possible faults:

- 1. An address does not access a certain cell

- 2. A cell is not accessed with a certain address

- 3. With a certain address, multiple cells are accessed

- 4. A certain cell can be accessed with multiple addresses

• Fault combinations

**T**UDelft

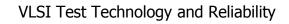

# 3. Faults: Read/Write logic (functional faults)

- Consist of faults in

- Sense amplifiers, Write drivers

- Pre-charge circuits, Multiplexes

- Etc

- They have never been analyzed

- Research map them into memory cell array faults

- Assuming a defect to be

- Complete open

- A short / bridges with very low resistance value

- Good coverage realized in the past (old technologies >0.1um)

**T**UDelft

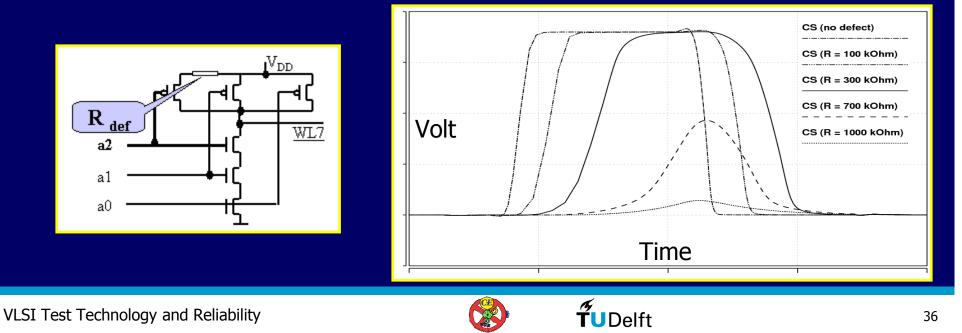

### 3. Faults: address decoder (delay/dynamic faults)

- Delay faults

- Word lines and bit lines have an increasing load and high capacitance

- Open defects are becoming dominant in new technologies

- $\Rightarrow$  Delay faults are becoming important

# 3. Faults: Read/Write logic (delay/dynamic faults)

- Consist of e.g.,:

- <u>Slow</u> Sense Amplifier Fault (SSAF)

- <u>Slow</u> Write Driver Fault (SWDF)

- <u>Slow</u> PRecharge circuit Fault (SPRF)

⇒Speed related faults

- Cannot be mapped nto memory cell array faults

- Require specific *operation sequences!*

- Requires specific *addressing direction!*

### VLSI Test Technology and Reliability (ET4076)

### Memory Testing: 4. Memory test development

Faculty: Section: Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Engineering Laboratory (CE)

### Contents ...

# **Topics:**

1. Test notation

How we can describe a memory test

2. Detection conditions

Fault model  $\rightarrow$  test requirements

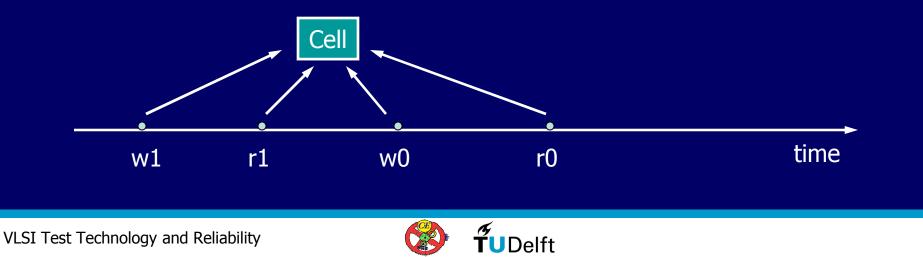

## **1.** Test notation... needed info

### How can we test a memory??

- We need:

- Operations (reads and writes)

- Data-in (what to write)

- Data-out (what to read)

- Addresses (which cells)

Addresses

$$N$$

,

Data-in  $B$ ,

Controls  $C$ ,

## **1.** Test notation... operations and data

- Operations and data

- wx = write data x

- rx = read data (expected value x)

- Example of a sequence

- (w1, r1, w0, r0)

- Write and read a cell with 1

- Then write and read a 0

## 1. Test notation... addresses

- Addressing:

- Up addressing: ↑ (i.e., from i=0 to N)

- Down addressing: ↓ (i.e., from i=N to 0)

- Irrelevant: 1

- Two dimensional arrays

- x-addressing: 1x

- y-addressing: (ly

- Example:  $\bullet$

- ↑ (w1, r1, w0, r0)

- Perform sequence going up!

- <u>MARCH ELEMENT</u>

x direction

C

Memory (c = cell)

С

С

С

С

С

С

## **1.** Test notation... march tests

- A march test = sequence of march elements

- Example: {(w0); ∩(r0, w1); ∪(r1)}

- Up or down, write 0 in all cells

- Going up, read 0, then write 1

- Going down, read 1

Memory (c = cell)

# **2. Detection conditions... what is it?**

- A **detection condition** = incomplete **march test**

- Detects a specific set of faults!

- Example:

- Transition Fault 1 (TF1) = <0w1/0/->

- To detect, start with 0, write 1, then read it!

- Detection condition

- \$(...0, w1, ..., r1, ...)

# 2. Detection conditions... single-cell faults

Single-cell FPs: <S/F/R>

S∈ {0,1,0w0,1w1,0w1,1w0, 0r0, 1r1}

F∈ {0,1}

$R \in \{0, 1, -\}$

- Compile the 12 FPs into 6 FMs

- 1. State Fault {1,2} (SF)/(SAF)

- 2. Write Disturb Fault {3,4} (WDF)

- 3. Transition Fault {5,6} (TF)

- 4. Incorrect Read Fault {7, 10} (IRF)

- 5. Read Destructive Fault {9, 12} (RDF)

- 6. Deceptive Read Destructive Fault {8,11} (DRDF)

| #  | S   | F | R | <s f="" r=""></s> |

|----|-----|---|---|-------------------|

| 1  | 0   | 1 | - | <0/1/->           |

| 2  | 1   | 0 | _ | <1/0/->           |

| 3  | 0w0 | 1 | - | <0w0/1/->         |

| 4  | 1w1 | 0 | - | <1w1/0/->         |

| 5  | 0w1 | 0 | - | <0w1/0/->         |

| 6  | 1w0 | 1 | - | <1w0/1/->         |

| 7  | 0r0 | 0 | 1 | <0r0/0/1>         |

| 8  | 0r0 | 1 | 0 | <0r0/1/0>         |

| 9  | 0r0 | 1 | 1 | <0r0/1/1>         |

| 10 | 1r1 | 1 | 0 | <1r1/1/0>         |

| 11 | 1r1 | 0 | 1 | <1r1/0/1>         |

| 12 | 1r1 | 0 | 0 | <1r1/0/0>         |

## 2. Detection conditions... single-cell faults

- State Faults (SF) =  $\{<0/1/->, <1/0/->\}$

- Incorrect Read Fault (IRF) =  $\{<0r0/0/1>, <1r1/1/0>\}$

- Read Destructive Fault (RDF)= {<0r0/1/1>, <1r1/0/0>}

*Condition: Read 0 and read 1 from each cell*

- Deceptive RDF (DRDF)= {<0r0/1/0>, <1r1/0/1>}

Apply a read to sensitize the fault, followed with a read to detect it

- Transition Fault (TF)= {<0w1/0/->, <1w0/1/->} Apply a transition write followed with a read operation

- Write Destructive Fault (WDF) = {<0w0/1/->, <1w1/0/->}

Apply a non-transition write followed with a read

# 2. Detection conditions... single-cell faults

### *Question: consider the test* Scan= {(w0); (r0); (w1); (r1)}

### Which faults (fault models) are not detected at all?

| a. SF   | b. IRF | c. RDF |

|---------|--------|--------|

| d. DRDF | e. TF  | f. WDF |

#### Which faults are partially detected?

| a. SF   | b. IRF | c. RDF |

|---------|--------|--------|

| d. DRDF | e. TF  | f. WDF |

How many single-cell faults does Scan detect?

| a. 12/12 | b. 11/12 | c. 10/12 |

|----------|----------|----------|

| d. 9/12  | e. 8/12  | f. 7/12  |

• Two-cell FPs: state

<S/F/R> = <Sa; Sv/F/R>Sa  $\in \{0,1\}, Sv \in \{0,1\}$ F  $\in \{0,1\}$ R  $\in \{0,1,-\}$

Compile the 4 FPs into 1 FM: State Coupling Fault (CFst)

| # | Sa | Sv | F | R | <sa; f="" r="" sv=""></sa;> |

|---|----|----|---|---|-----------------------------|

| 1 | 0  | 0  | 1 | - | <0; 0/1/->                  |

| 2 | 0  | 1  | 0 | - | <0; 1/0/->                  |

| 3 | 1  | 0  | 1 | - | <1; 0/1/->                  |

| 4 | 1  | 1  | 0 | - | <1; 1/0/->                  |

1. State Coupling Faults CFst= {<0; 0/1/->, <0; 1/0/->, <1; 0/1/->, <1; 1/0/->}

- *Sensitization*: the four states of any two cells are reached •

- *Detection*: a read operation is applied to each cell within each state •

- Example:{(w0); (r0); (w1); (r1); *consider cells Ci and Cj where i*<*j* • M0 M3

M1 M2

| # | Mi | State | Oper.    | State | Effect                                            |

|---|----|-------|----------|-------|---------------------------------------------------|

| 1 | M0 |       | w0 to Ci | 0 -   | -                                                 |

| 2 | M0 | 0 -   | w0 to Cj | 00    | <0; 0/1/->i,j and <0; 0/1/->j,i <i>sensitized</i> |

| 3 | M1 | 00    | r0 to Ci | 00    | <0; 0/1/->j,i <i>detected</i>                     |

| 4 | M1 | 00    | r0 to Cj | 00    | <0; 0/1/->i,j <i>detected</i>                     |

| 5 | M2 | 00    | w1 to Ci | 10    | <0; 1/0/->j,i and <1; 0/1/->i,j <i>sensitized</i> |

| 6 | M2 | 10    | w1 to Cj | 11    | <1; 1/0/->i,j and <1; 1/0/->j,i <i>sensitized</i> |

| 7 | M3 | 11    | r1 to Ci | 11    | <1; 1/0/->j,i <i>detected</i>                     |

| 8 | M3 | 11    | r1 to Cj | 11    | <1; 1/0/->i,j <i>detected</i>                     |

|   |    |       |          |       |                                                   |

**Fault Coverage FC=4/8 sub-Fault Primitives**

### Two-cell FPs: 1PF2v (v-cell accessed)

Sa  $\in$  {0,1} Sv  $\in$  {0w0,1w1,0w1,1w0, 0r0, 1r1} F  $\in$  {0,1} R  $\in$  {0,1,-} x  $\in$  {0,1}

Compile the 24 FPs into 5 FMs: CF= Coupling Fault 1. Write Disturb CF {1,2} (CFwd) 2. Transition CF {3,4} (CFtr) 3. Incorrect Read CF {5,8 } (CFir) 4. Read Destructive CF {7,10}(CFrd) 5. Deceptive CFrd {6,9} (CFdr)

| #  | Sa | Sv  | F | R | <s f="" r=""></s>          |

|----|----|-----|---|---|----------------------------|

| 1  | x  | 0w0 | 1 | - | <x; -="" 0w0="" 1=""></x;> |

| 2  | x  | 1w1 | 0 | - | <x; -="" 0="" 1w1=""></x;> |

| 3  | X  | 0w1 | 0 | - | <x; -="" 0="" 0w1=""></x;> |

| 4  | x  | 1w0 | 1 | - | <x; -="" 1="" 1w0=""></x;> |

| 5  | X  | 0r0 | 0 | 1 | <x; 0="" 0r0="" 1=""></x;> |

| 6  | x  | 0r0 | 1 | 0 | <x; 0="" 1="" r0r=""></x;> |

| 7  | X  | 0r0 | 1 | 1 | <x; 0r0="" 1=""></x;>      |

| 8  | X  | 1r1 | 1 | 0 | <x; 0="" 1="" 1r1=""></x;> |

| 9  | x  | 1r1 | 0 | 1 | <x; 0="" 1="" 1r1=""></x;> |

| 10 | X  | 1r1 | 0 | 0 | <x; 0="" 1r1=""></x;>      |

### 2. Incorrect Read Coupling Faults

- CFir= {<0; 0r0/0/1>, <0; 1r1/1/0>, <1; 0r0/0/1>, <1; 1r1/1/0>}

- Sensitization/ Detection: the four states of any two cells are reached, and a read operation is applied to each cell within each state.

- Example: {↑(w0); ↑(r0); ↑(w1); ↑(r1)} ; *consider cells Ci and Cj where i<j*

| # | Mi | State | Oper.    | State |

|---|----|-------|----------|-------|

| 1 | M0 |       | w0 to Ci | 0 -   |

| 2 | M0 | 0 -   | w0 to Cj | 00    |

| 3 | M1 | 00    | r0 to Ci | 00    |

| 4 | M1 | 00    | r0 to Cj | 00    |

| 5 | M2 | 00    | w1 to Ci | 10    |

| 6 | M2 | 10    | w1 to Cj | 11    |

| 7 | M3 | 11    | r1 to Ci | 11    |

| 8 | M3 | 11    | r1 to Cj | 11    |

|   |    |       |          |       |

**Effect**

<0; 0r0/0/1>j,i *sensitized & detected* <0; 0r0/0/1>i,j *sensitized & detected*

<1; 1r1/1/0>j,i *sensitized & detected* <1; 1r1/1/0>i,j *sensitized &detected*

#### **Result: FC=4/8 sub-Fault Primitives**

#### 3. Read Destructive Coupling Faults

• CFrd= {<0; 0r0/1/1>, <0; 1r1/0/0>, <1; 0r0/1/1>, <1; 1r1/0/0>}

- *Sensitization/ Detection:* the four states of any two cells are reached, and a read operation is applied to each cell within each state.

- Example: {↑(w0); ↑(r0); ↑(w1); ↑(r1)} ; *consider cells Ci and Cj where i<j*

| # Mi | State | Oper.    | State | Effect                                           |

|------|-------|----------|-------|--------------------------------------------------|

| 1 M0 |       | w0 to Ci | 0 -   | -                                                |

| 2 M0 | 0 -   | w0 to Cj | 00    | -                                                |

| 3 M1 | 00    | r0 to Ci | 00    | <0; 0r0/0/1>j,i <i>sensitized &amp; detected</i> |

| 4 M1 | 00    | r0 to Cj | 00    | <0; 0r0/0/1>i,j <i>sensitized &amp; detected</i> |

| 5 M2 | 00    | w1 to Ci | 10    | -                                                |

| 6 M2 | 10    | w1 to Cj | 11    | -                                                |

| 7 M3 | 11    | r1 to Ci | 11    | <1; 1r1/1/0>j,i <i>sensitized &amp; detected</i> |

| 8 M3 | 11    | r1 to Cj | 11    | <1; 1r1/1/0>i,j <i>sensitized &amp;detected</i>  |

#### **Result: FC=4/8 sub-Fault Primitives**

- 4. Deceptive Read Destructive Coupling Faults

- CFdr= {<0; 0r0/1/0>, <0; 1r1/0/1>, <1; 0r0/1/0>, <1; 1r1/0/1>}

- *Sensitization:* the four states of any two cells are reached, and a read operation is applied to each cell within each state.

- *Detection*: **another read** is applied to each cell within each state

- Example: {<sup>↑</sup>(w0); <sup>↑</sup>(r0); <sup>↑</sup>(w1); <sup>↑</sup>(r1)} ; *consider cells Ci and Cj where i<j*

| # | Mi | State | Oper.    | State | Effect                            |

|---|----|-------|----------|-------|-----------------------------------|

| 1 | M0 |       | w0 to Ci | 0 -   | -                                 |

| 2 | M0 | 0 -   | w0 to Cj | 00    | -                                 |

| 3 | M1 | 00    | r0 to Ci | 00    | <0; 0r0/1/0>j,i <i>sensitized</i> |

| 4 | M1 | 00    | r0 to Cj | 00    | <0; 0r0/1/0>i,j <i>sensitized</i> |

| 5 | M2 | 00    | w1 to Ci | 10    | -                                 |

| 6 | M2 | 10    | w1 to Cj | 11    | -                                 |

| 7 | M3 | 11    | r1 to Ci | 11    | <1; 1r1/0/1>j,i <i>sensitized</i> |

| 8 | M3 | 11    | r1 to Cj | 11    | <1; 1r1/0/1>i,j <i>sensitized</i> |

#### **Result: FC=0/8 sub-Fault Primitives**

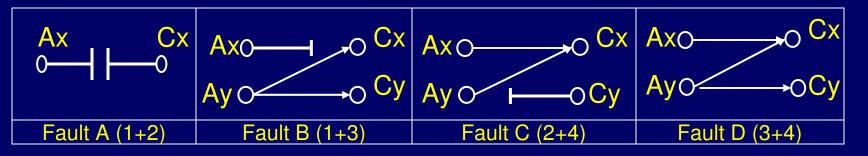

# **2. Detection conditions... AFs**

• Address decoder faults:

**Detection condition**

A test detects AFs iff it contains the following two march elements; x=0 or x=1:

- $(r_{x}, ..., w_{x}^{*}, [r_{x}^{*}]^{h})$

- $\Downarrow$  (r $x^*$ , ..., wx, [rx]<sup>h</sup>)

*h* for hammer;  $h \ge 1$

Question: what is the optimal test detecting all AFs?

• ∩ (r*x*, ..., w*x*\*, [r*x*\*]<sup>*h*</sup>) • ↓ (r*x*\*, ..., w*x*, [r*x*]<sup>*h*</sup>)

- . { $(\uparrow(r1,w1,r1); \downarrow(r1,w0,r0)$ }?

- 2. {îî(r0,w1,r1); ↓(r1,w0,r0) }?

- 3. { $(m0); (r0,w1,r1); \cup (r1,w0,r0)$  }?

### VLSI Test Technology and Reliability (ET4076)

### Memory Testing: 5. Well-known memory tests

Faculty: Section: Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Engineering Laboratory (CE)

- Most know Ad-hoc test:

- Scan= Zero-One Test

- Checkerboard

- GalPat

- Walking 1/0

- Typically until 1980's

- Absence of formal fault models

- Not acceptable due to

- Low fault coverage (Scan/ Checkerboard)

- High cost (GalPat/ Walking 1/0)

#### Scan= Zero-One Test

Write 0 in all cells (starting at cell 0)

Read all cells (starting at cell 0)

Write 1 in all cells (starting at cell 0)

Read all cells (starting at cell 0)

- In short notation: {<sup>↑</sup>(w0); <sup>↑</sup>(r0); <sup>↑</sup>(w1); <sup>↑</sup>(r1)}

- Test length: 4n => O(n): *linear time complexity*

- Low Fault coverage:

- 7/12 single-cell faults (1PF1s)

- 18/72 two-cell faults (1PF2s)

- No address decoder faults (AFs)

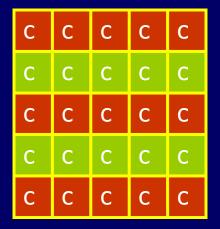

#### Checkerboard

- Divide the memory cell into two groups, say cells-1 and cells-2

Write 1 in cells-1 and 0 in cells-2

Read all cells

Write 0 in all cells-1 and 1 in cells-2.

Read all cells

0 1

- Test length: 4n => O(n)

- Short Notation: { $(w1_i, w0_{i+1}); (r1_i, r0_{i+1});$  $(w0_i, w1_{i+1}); (r0_i, r1_{i+1})$ where  $0 \le i < n-2$

| 1 | 0 | 1 | 0 |

|---|---|---|---|

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

Memory array

• Low fault coverage (similar to Scan)

### Galpat, Walking 1/0

→ Time complexity: O(n<sup>2</sup>)

#### Low fault coverage

}

Galpat: 10/12 1PFs, 44/72 1PF2s, no AFs

Walking 1/0: 8/12 1PFs, 40/72 1PF2s, no AFs

Read-Action Galpat for cell=0 to n-1 (base-cell excluded) { if A[cell]≠d then output ("ERROR") if A[base-cell]≠d\* then output ("ERROR")

Read-Action Walking 1/0 for cell=0 to n-1 (base-cell excluded) { if A[cell]≠d then output ("ERROR")

*if A[base-cell]≠d\* then output ("ERROR")*

}

## 5. Memory tests... Ad-hoc vs march

- Ad-hoc tests:

- Low fault coverage, and/or

- High time complexity

- Industrially not acceptable for serious test purposes

- Based on speculations not on fault models

- March tests:

- + Based on fault models

- + Linear time complexity

- + Acceptable fault coverage

- With newer technologies

- New defects

- New fault models required

- New advanced tests

### 5. Memory tests... march tests

List of some well known march tests

- MATS+ [Nair, 79]: {\$(w0); ↑(r0,w1); ↓(r1,w0)}

- MATS++ [Breuer, 76}: {\$(w0); ↑(r0,w1); ↓(r1,w0,r0)}

- PMOVI [de Jonge, 76] {\u03c8(w0); \u03c8(r0,w1,r1); \u03c8(r1,w0,r0); \u03c8(r0,w1,r1); \u03c8(r1,w0,r0)}

- March B [Suk, 81]: {\$\$(w0); \$\$(r0,w1,r1,w0,r0,w1); \$\$(r1,w0,w1); \$\$(r1,w0,w1,w0); \$\$\$\$\$\$\$\$\$\$\$\$\$\$\$(r0,w1,w0)\$\$\$

- March C- [van de Goor, 91]: {\$\$(w0); ↑\$(r0,w1); ↑\$(r1,w0); ↓\$(r0,w1); ↓\$(r1,w0); \$\$(r0)}

## 5. Memory tests... march tests

- Advanced tests: fault primitive-based

- High fault coverage

- Cover realistic faults

- Linear with the size of the memory

- An example of advanced tests based on fault primitives is as follows

- March MSS [Hamdioui 02, Harutunvan, 05] (18n): test for all static simple faults

| March MSS={           |    |

|-----------------------|----|

| ≎(w0);                | M0 |

| <b>(r0,r0,w1,w1);</b> | M1 |

| <b>(r1,r1,w0,w0);</b> | M2 |

| ∜(r0,r0,w1,w1);       | M3 |

| ∜(r1,r1,w0,w0);       | M4 |

| <b>û(r0)</b> }        | M5 |

## 5. Memory tests... march tests

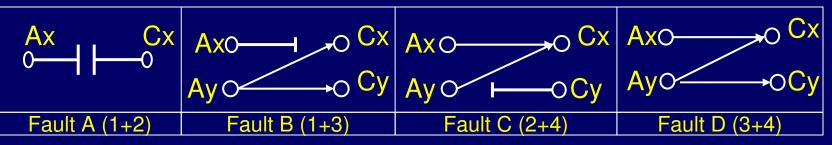

| Fault Model                   | MATS+<br>(5n) | March C-<br>(10n) | PMOVI<br>(13n) | March SR<br>(14n) | March G<br>(23n) | Ham.<br>(49n) | Galpat<br>O(n²) | March MSS<br>(22n) |

|-------------------------------|---------------|-------------------|----------------|-------------------|------------------|---------------|-----------------|--------------------|

| SAF                           | 2/2           | 2/2               | 2/2            | 2/2               | 2/2              | 2/2           | 2/2             | 2/2                |

| TF                            | 1/2           | 2/2               | 2/2            | 2/2               | 2/2              | 2/2           | 2/2             | 2/2                |

| WDF                           | 0/2           | 0/2               | 0/2            | 0/2               | 0/2              | 2/2           | 0/2             | 2/2                |

| IRF/ RDF                      | 2/2           | 2/2               | 2/2            | 2/2               | 2/2              | 2/2           | 2/2             | 2/2                |

| DRDF                          | 0/2           | 0/2               | 2/2            | 2/2               | 0/2              | 2/2           | 0/2             | 2/2                |

| CFst                          | 4/8           | 8/8               | 8/8            | 8/8               | 6/8              | 8/8           | 8/8             | 8/8                |

| CFds [r <i>x</i> ]            | 3/8           | 8/8               | 8/8            | 8/8               | 7/8              | 8/8           | 8/8             | 8/8                |

| CFds [ <i>x</i> w <i>x*</i> ] | 3/8           | 8/8               | 7/8            | 8/8               | 8/8              | 7/8           | 4/8             | 8/8                |

| CFds [ <i>x</i> w <i>x</i> ]  | 0/8           | 0/8               | 0/8            | 0/8               | 0/8              | 7/8           | 0/8             | 8/8                |

| CFtr                          | 2/8           | 8/8               | 8/8            | 8/8               | 4/8              | 8/8           | 4/8             | 8/8                |

| CFwd                          | 0/8           | 0/8               | 0/8            | 0/8               | 0/8              | 8/8           | 0/8             | 8/8                |

| CFrd/ CFir                    | 4/8           | 8/8               | 8/8            | 8/8               | 4/8              | 8/8           | 8/8             | 8/8                |

| CFdr                          | 0/8           | 0/8               | 6/8            | 4/8               | 0/8              | 6/8           | 0/8             | 8/8                |

| Total                         | 29/84         | 56/84             | 63/84          | 62/84             | 57/84            | 80/84         | 54/84           | 84/84              |

# **Trends in memory testing**

- Dynamic faults/ address decoder delay faults

- Intra-word faults

- Faults in the periphery circuits (speed related faults)

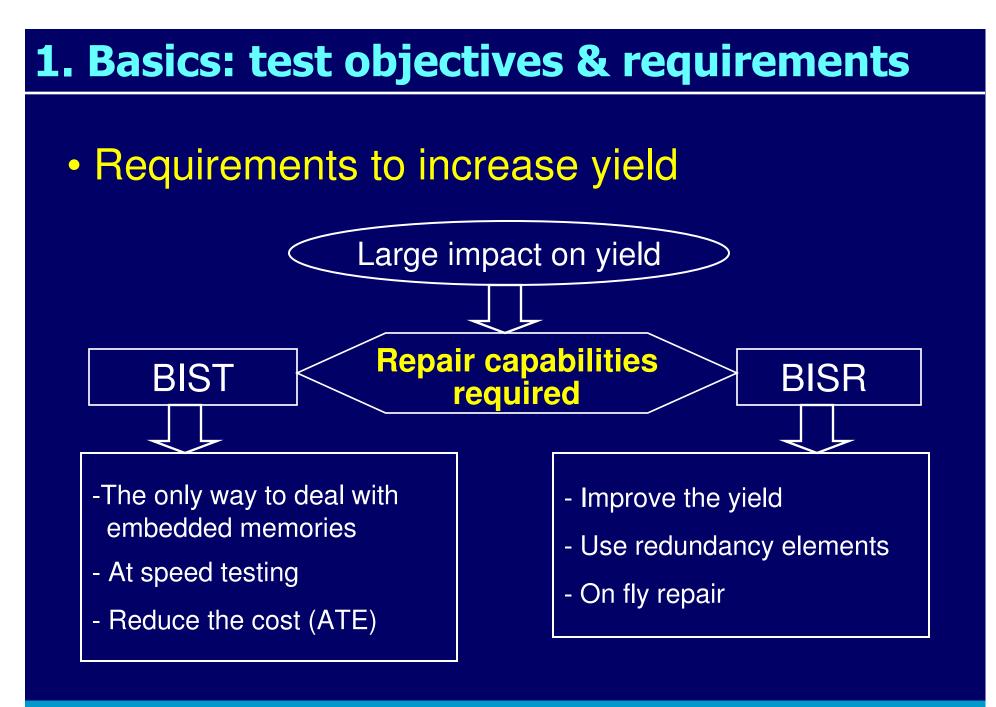

- Built-in-Self-Testing (BIST) and repair (BISR)

- On-line testing/Built-in-self-correction (BISC)/soft faults/errors

- Reliability in memories

- Testing ROMs (FLASH memories)

### Summary

- Memory testing is very important

- Large share of SoC area, large impact on quality, yield and reliability

- Memory Faults classified into three types

- Memory cell array faults

- Single cell versus coupling faults

- Address decoder faults

- Peripheral circuits faults

- Static faults versus dynamic faults

- Three classes of memory test algorithms

- Ad-hoc tests

- March tests

- Fault-primitive based tests

- Major challenges

- Speed related faults

- Repair, diagnosis, ...