**Energy research Centre of the Netherlands**

# **Crystalline Si Photovoltaics**

**Arthur Weeber**

#### **Outline**

- Short introduction ECN

- Introduction ECN Solar Energy

- General Si solar cells

- Crystalline Si Photovoltaics

- Feedstock

- Wafering

- Cell processing

- Module technology

- Costs and environmental

- Summary

### **Targets ECN research**

**Transition to renewable energy supply:**

efficiency improvement

development of renewable energy

clean use of fossil fuels

maximum reliability

minimum environmental burden

optimal cost effectiveness

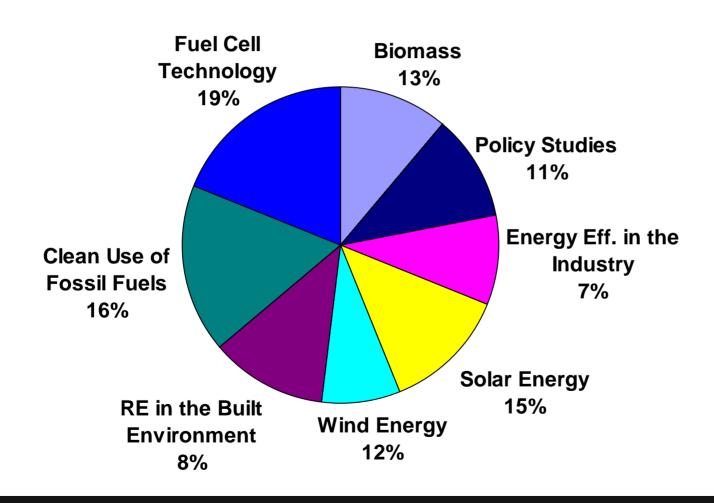

### **ECN Programme units**

Strategically Policy Studies

Energy savings Energy Efficiency in Industry

Renewable Energy in the Built Environment

Renewable energy Solar Energy

Wind Energy

Biomass, Coal & Environmental research

Clean use fossil fuels Hydrogen & Clean fossil fuels

Support Engineering & Services

#### **Turnover share per unit (2005)**

**Energy research Centre of the Netherlands**

# **ECN Solar Energy**

### **Solar Energy**

- Silicon Photovoltaics

- Thin-Film Photovoltaics

- PV Module Technology

#### Objective:

- Price of solar electricity in 2015 the same as consumer electricity price, and after that even lower

- High efficiency

- Reduction of material use

- Cost effective and environmental friendly processes and products

- Long lifetime of the modules

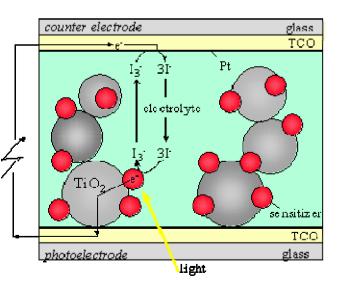

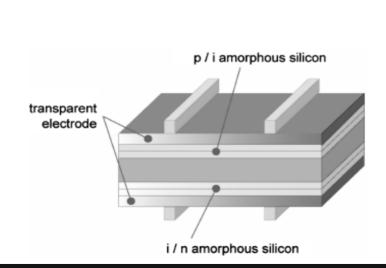

#### **Thin-film photovoltaics**

- Sensitised oxides

- efficiency, stability, manufacturing technology

- solid state version: in 2015 η=8% for 10x10 cm<sup>2</sup>

device with >10 year outdoor stability

#### **Thin-film photovoltaics**

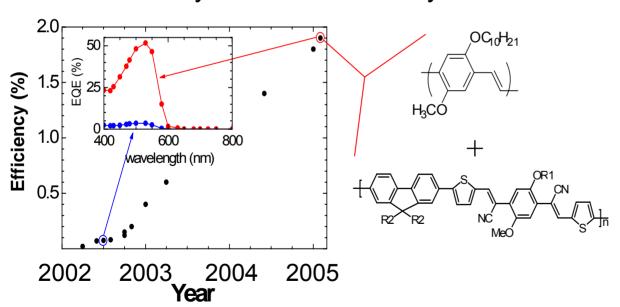

- Organic solar cells

- device fabrication, efficiency and stability

- in 2015  $\eta$ =8% for 10x10 cm<sup>2</sup> device with >10 year outdoor stability

Collaboration of ECN, TNO

#### **Thin-film photovoltaics**

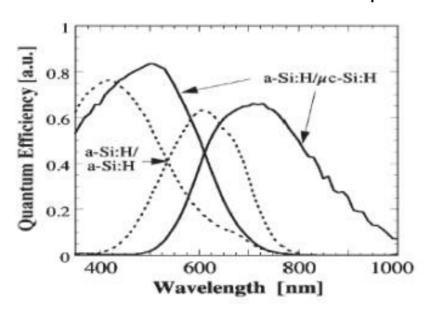

- Thin-film silicon

- R-2-R deposition of (n,i,p) silicon on foils

- Development of thin-film Si tandems

- In 2015 a 0.3x1 m<sup>2</sup> PV module η=12% at 0.8€/Wp

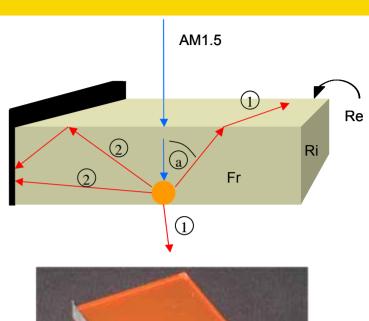

#### **New concepts**

- improved spectrum utilization

- flat plate concentrator

#### **PV systems**

- grid interaction

- system design & monitoring

- standards and guidelines

# Crystalline Si PV technology

#### Objective:

- Price of solar electricity in 2015 the same as consumer electricity price, and after that even lower

- High efficiency

- 18% module efficiency for crystalline Si PV

- Reduction of material usage

- Thin wafers (<150 μm compared to current >240 μm)

- Cost effective and environmental friendly processes and products

- Long lifetime of the modules (>30 yr for crystalline Si)

- Energy Pay Back Time < 1 yr</li>

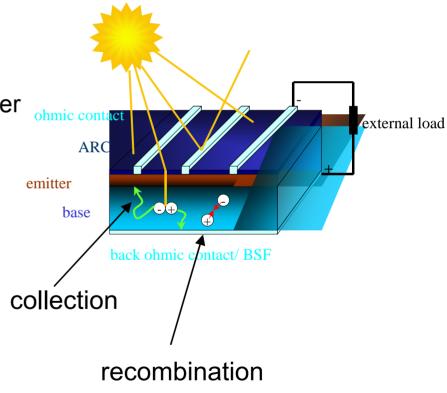

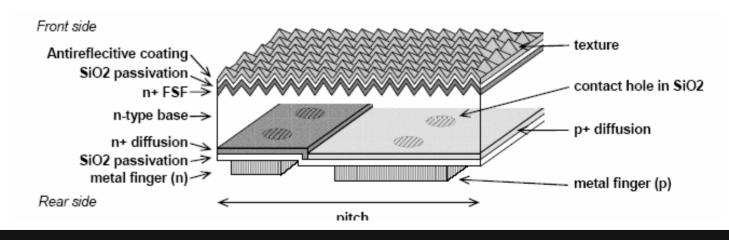

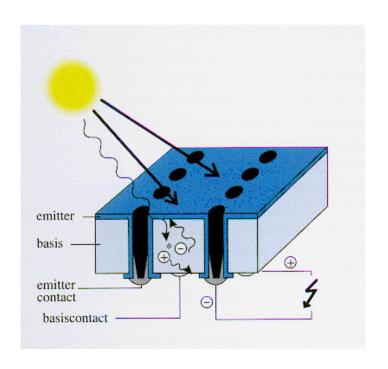

#### **Cell structure**

Crystalline silicon solar cell (minority carrier device)

- Base: B doped Si (p-type)

- Emitter: P doped layer (n-type)

- Recombination losses in base and emitter

- Voltage over pn junction

- Metallization for contacts

- Shading losses

- Resistance losses

- Antireflection coating to enhance current

- Surfaces: recombination losses

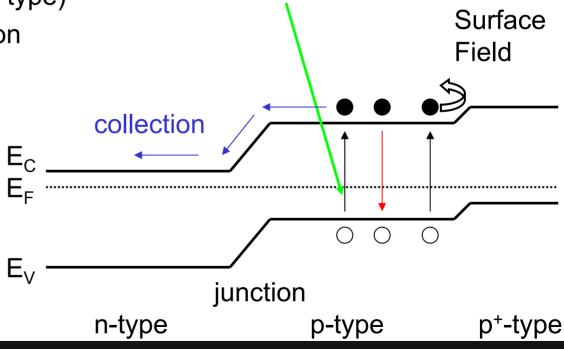

#### **Cell structure**

Crystalline silicon solar cell

- Base: B doped Si (p-type)

- Emitter: P doped layer (n-type)

- Voltage over pn junction

- Recombination losses

- BSF: p<sup>+</sup> doped layer

- Highly doped

- Reduced recombination

photon

recombination

Back

#### **Cell structure**

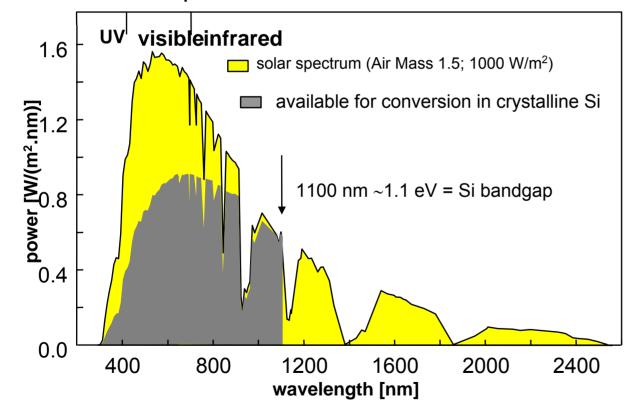

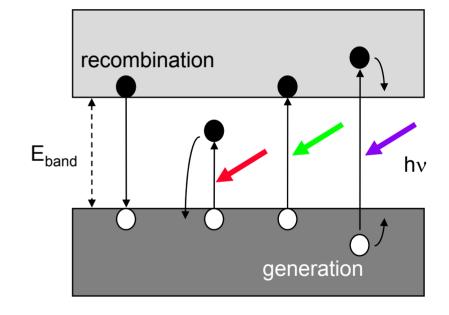

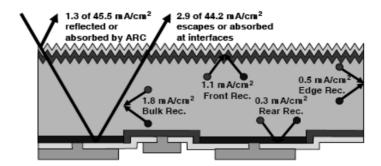

Losses in crystalline silicon solar cell

- Colour mismatchFundamental recombination

- Additional recombination

- Impurities, defects, surfaces

- Shading

- Reflection, absorption and transmission

- Absorption at the rear

- Resistance

- Non-ideal band gap

Crystalline Si solar cell: η=13-20%

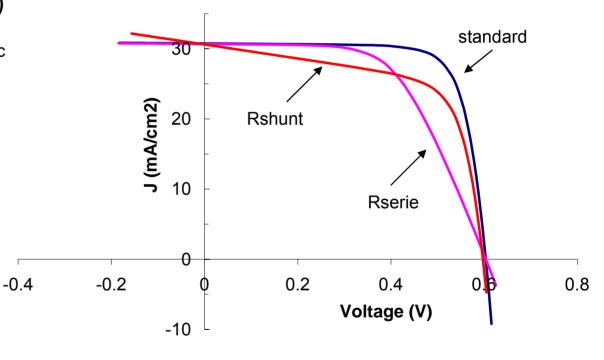

#### **Cell characterization**

- Current Voltage (IV curve)

- Open circuit voltage V<sub>oc</sub>

- Short circuit current J<sub>sc</sub>

- Efficiency

- Resistance losses

#### **Cell characterization**

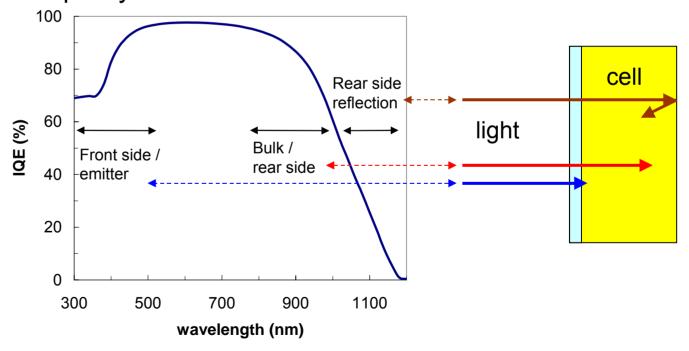

- Internal Quantum Efficiency IQE

- IQE=collected carriers / absorbed photons

- Depth profile cell quality

## Crystalline Si PV technology

- Feedstock

- Effect impurities on cell output

- Wafers

- Monocrystalline Si

- Multicrystalline Si

- Cell technology

- High efficiency with industrial in-line processing

- Module Technology

- Module design integrated with cell concept

- Simple interconnection and encapsulation

- Costs and environmental aspects

# Crystalline Si PV technology

- Feedstock

- Effect impurities on cell output

- Wafers

- Monocrystalline Si

- Multicrystalline Si

- Cell technology

- High efficiency with industrial in-line processing

- Module Technology

- Module design integrated with cell concept

- Simple interconnection and encapsulation

- Costs and environmental aspects

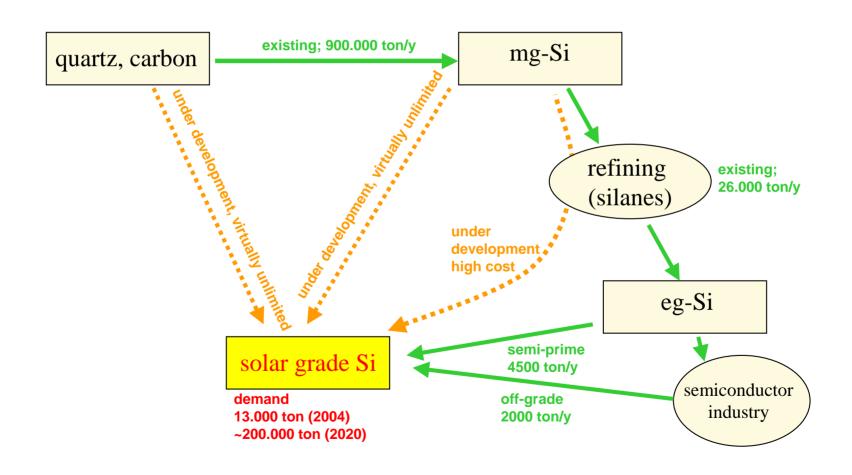

# **Feedstock production**

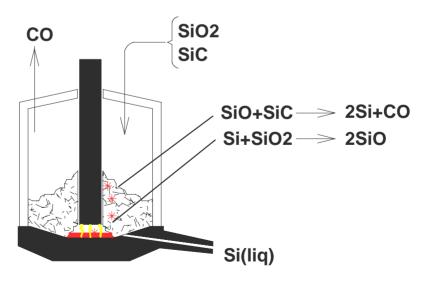

## **Feedstock production**

- Direct route: SOLSILC process

- plasma furnace: SiC from pure SiO<sub>2</sub> and pure C pellets of SiC and SiO<sub>2</sub>

Si(L)

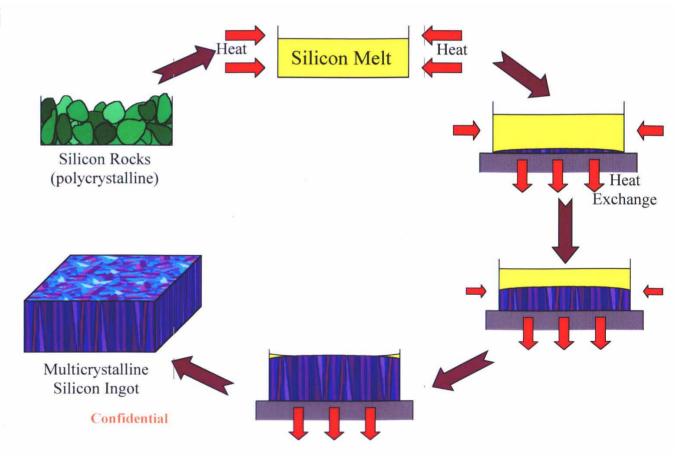

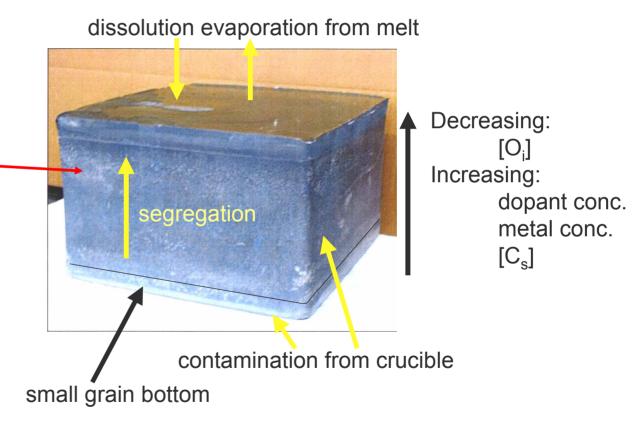

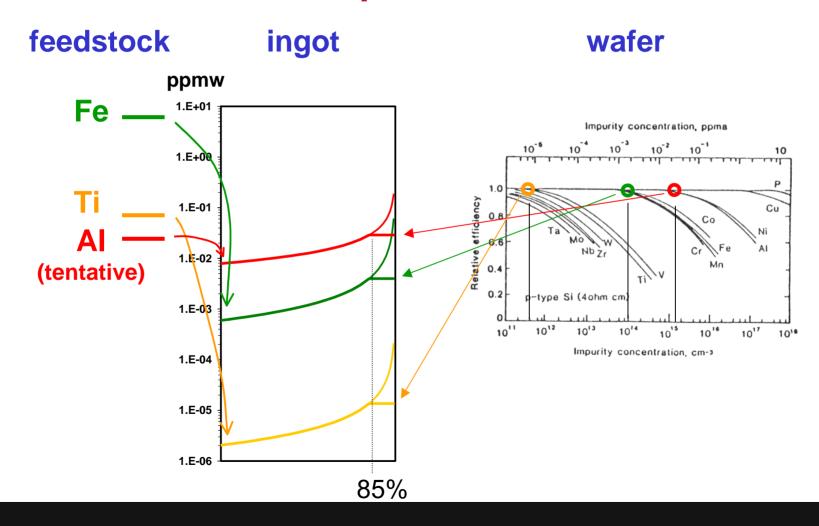

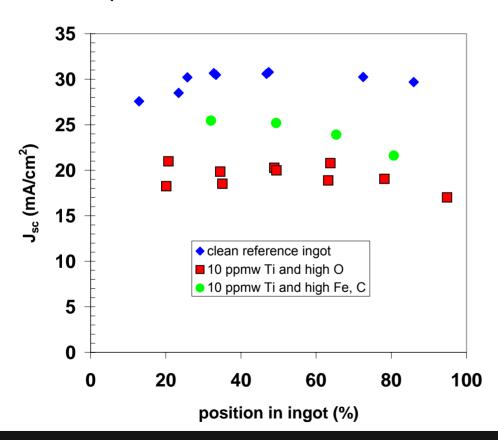

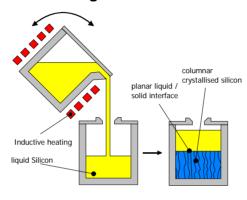

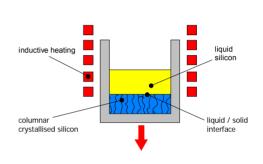

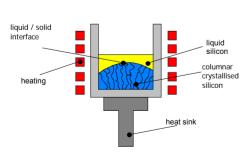

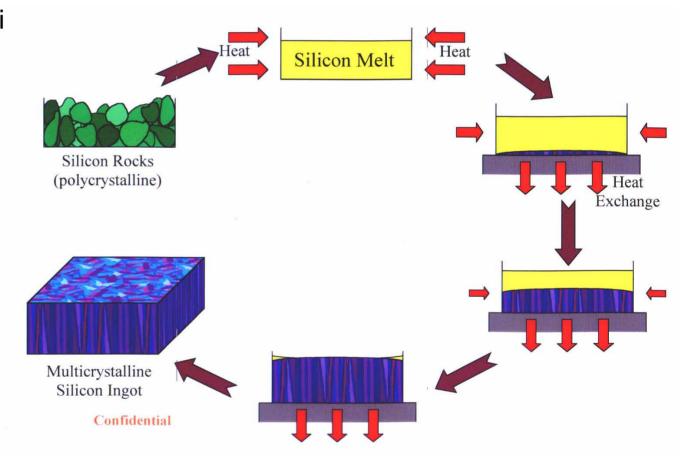

## Feedstock: ingot growth

Multicrystalline Si ingot growth

- Feedstock

- Melting

- Crystallization

- Ingot -

- Sawing

- Wafer

Impurities added to feedstock

Effect Ti and O on cell output clearly visible

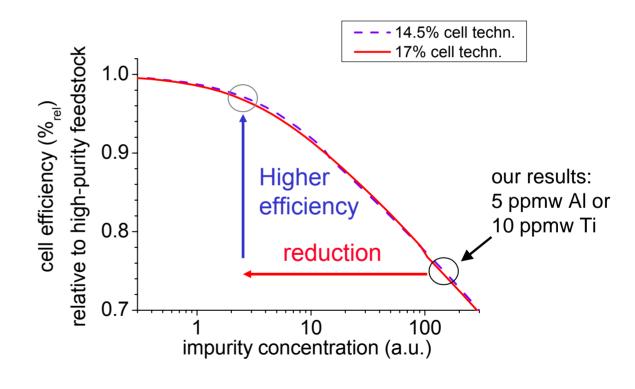

#### Impurities added to feedstock

- Ingot growth

- Wafering

- Cell processing

- Characterization

- Model development

- $1/L_{eff}^2 \propto 1/\tau \propto C_{imp}$

- Segregation during growth

- Solar cell modeling

- Needed to define Solar Grade Si

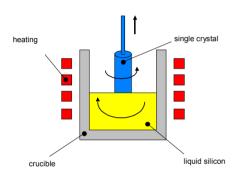

### Pulling of Single Crystals (Czochralski)

**Casting of Silicon Blocks**

**Bridgman Solidification**

Heat Exchange Method

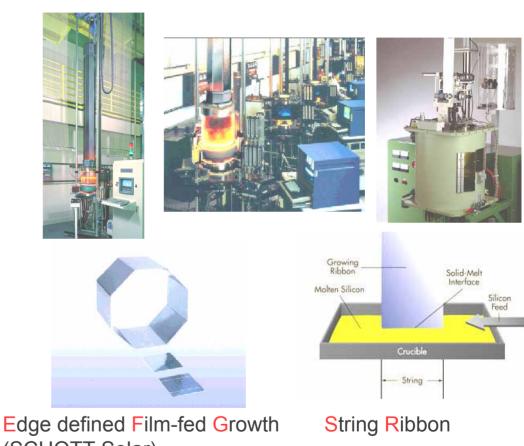

Edge defined Film fed Growth

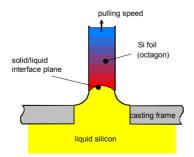

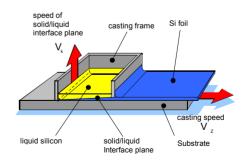

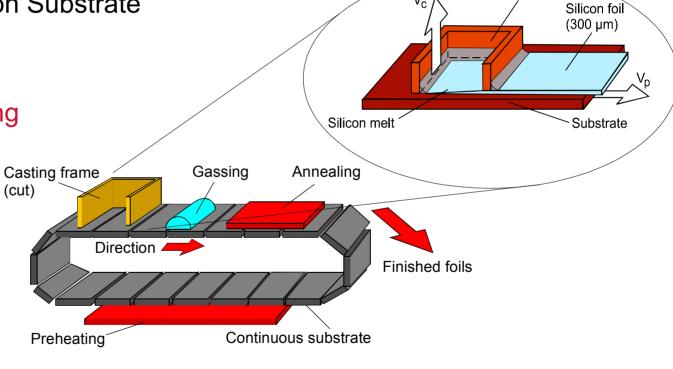

#### Ribbon Growth on Substrate

Multicrystalline Si ingot growth

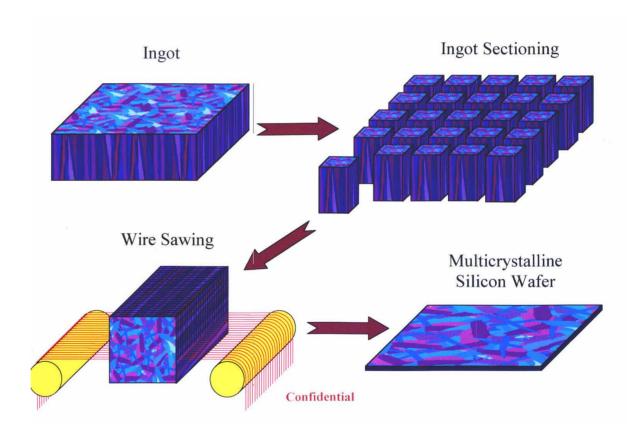

From ingot to mc-Si wafer

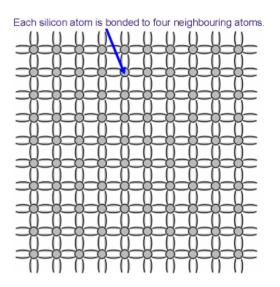

- High quality monocrystalline Si material

- Low impurity concentration

- Low defect concentration

- Higher efficiency (15-17% in industry, 20% pilot)

- Higher costs per cell

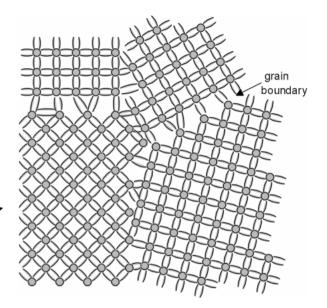

- Lower quality multicrystalline Si material (mc-Si)

- Higher impurity concentration

- More defects

- Lower efficiency (13-15% in industry, >16% pilot)

- Lower costs per cell

- For both technologies: high sawing losses (about 50%!)

- Ribbon technologies (multicrystalline Si)

- Substrate growing and crystallization in the same direction

ECN's ribbon technology

Ribbon Growth on Substrate

RGS

Substrate growing perpendicular to crystallization

Frame

#### Ribbons:

Better use of Si material (about factor 2)

#### But

- Lower initial material quality

- Lower efficiencies

- EFG/SR: about 14% (industry)

- RGS: about 13% (lab)

- Very high throughput

| Material | Pull<br>Speed<br>[cm/min] | Through-<br>put<br>[cm²/min] | Furnaces<br>per 100<br>MW |

|----------|---------------------------|------------------------------|---------------------------|

| EFG      | 1.7                       | 165                          | 100                       |

| SR       | 1-2                       | 5-16                         | 1175                      |

| RGS      | 600                       | 7500                         | 2-3                       |

<sup>\*[</sup>J. Kalejs, E-MRS 2001 Strasbourg]

# Wafer Technology

RGS cell efficiencies using industrial process

- Average efficiency 12.5%.

- Current top efficiency 13%<sup>confirmed</sup>

- High efficiency lab processing 14.4%<sup>confirmed</sup>

- ~100 µm thin RGS wafer made

- Efficiency around 11%

- 2.9 g Si/Wp (nowadays ~10 g Si/Wp)

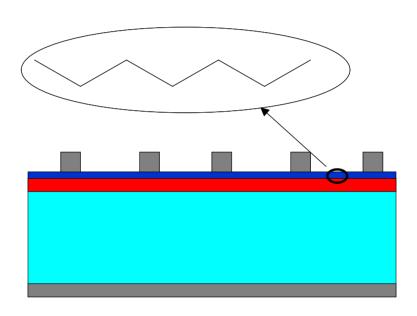

- Saw damage removal

- Texturing for enhanced light coupling (better efficiencies)

- Emitter diffusion

- Material improvement by gettering

- SiN<sub>x</sub> deposition as antireflection layer

- Material improvement by passivation

- Reduced surface recombination (surface passivation)

- Metallization

- Ag front side

- Al rear side (so-called Back Surface Field)

- Sintering for contact formation

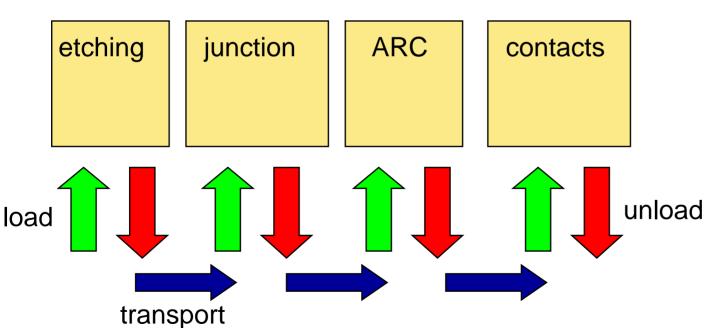

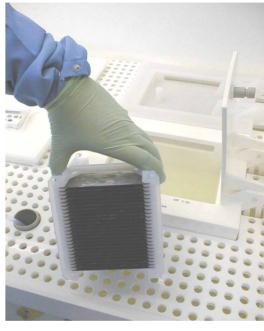

#### **Batch processing**

- Wafers in carriers

- Each process step well controlled

- Used for high efficiency processing

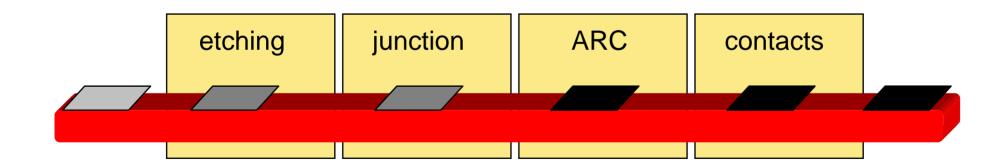

#### **ECN's inline processing**

Horizontal wafer transport on belts (wafer in; cell out)

- No wafer carriers

- Large and thin wafers easier to handle (cost reduction)

#### **Examples from industry**

Batch processing BP Solar

In-line processing SCHOTT Solar

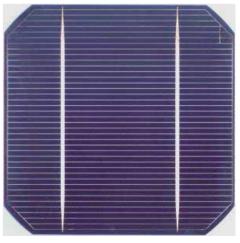

#### **ECN Baseline process**

- Multicrystalline p-type Si

- Acidic texturing / saw damage removal

- P diffusion using belt furnace

- Deposition of SiN<sub>x</sub>

- Metallization (Ag front, full Al rear)

- Simultaneous sintering both contacts

#### **Results**

Processing complete columns of wafers during two years

- Average 16%

- In industry about 15%

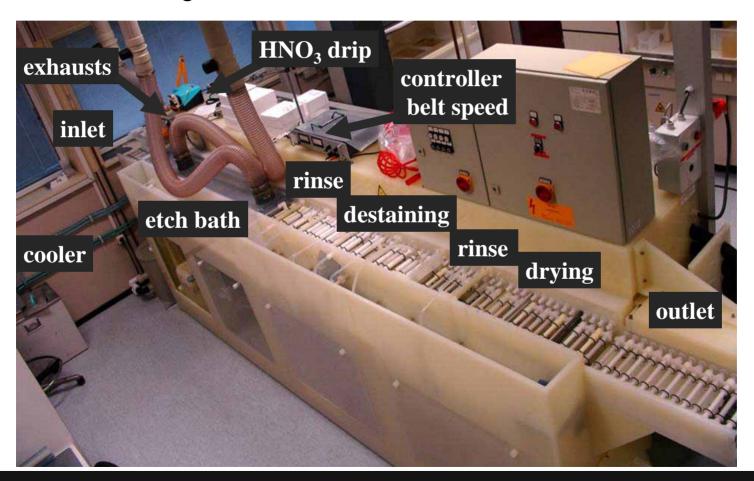

Wet chemical etching

Sintering contacts

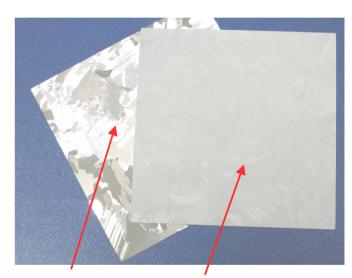

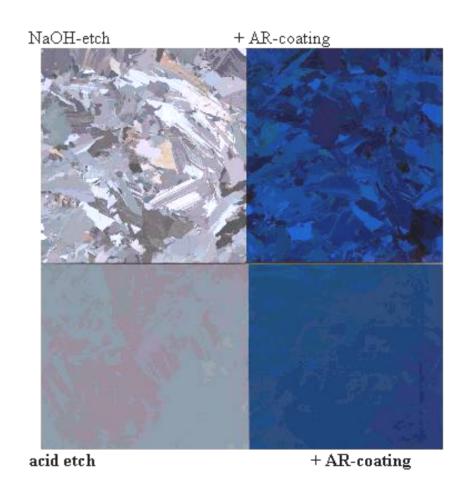

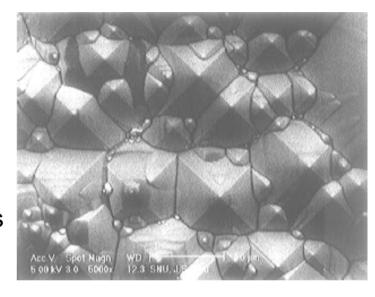

Acidic texturing of mc-Si

Alkaline and acidic etch

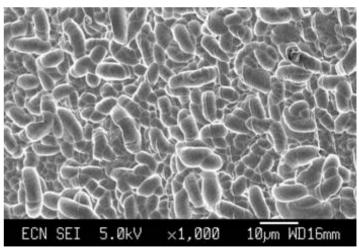

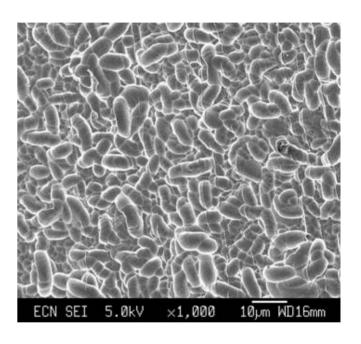

Acidic texturing of mc-Si

Acidic texturing of mc-Si

- Lower reflection, higher efficiency

- About 0.5% absolute

- Better appearance

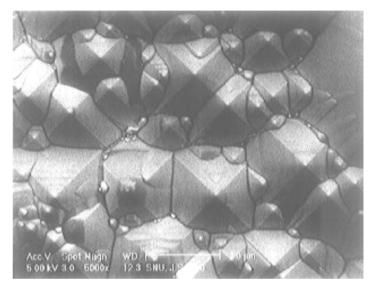

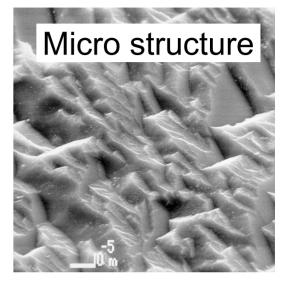

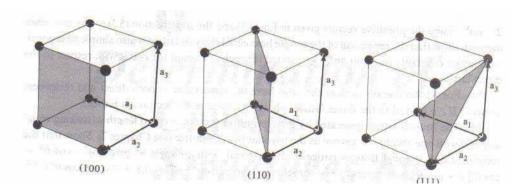

Surface structure texturing Si

- Monocrystalline Si

- Alkaline etching (NaOH or KOH)

- Anisotropic etching

- (111) planes slowest etching rate

- Pyramids on (100) substrates

- Multicrystalline Si

- HF/HNO<sub>3</sub> etching

- Isotropic etching

- Random structure

Alkaline etching of Si Si + OH<sup>-</sup> + H<sub>2</sub>O  $\rightarrow$  SiO<sub>3</sub><sup>2-</sup> + H<sub>2 qas</sub>

- Higher concentrations and higher T

- Almost isotropic etching

- High etching rate

- Used to remove saw damage (5-10 μm)

- High reflectance (~30%)

#### Alkaline etching of Si

- Lower concentrations and lower T

- Anisotropic etching

- (111) planes slowest etching rate

- Pyramids as texture on (100) substrates

- Low reflectance (~10%)

- But, low etching rate

Acidic etching of Si

Mixture HF/HNO<sub>3</sub>

Oxidation

$$3 \text{ Si} + 4 \text{ HNO}_3 \rightarrow 3 \text{ SiO}_2 + 4 \text{ NO}_{gas} + 2 \text{ H}_2\text{O}$$

Oxide removal

$$SiO_2 + 4 HF \rightarrow SiF_{4 gas} + 2 H_2O$$

- Obtained surface morphology depends on composition

- Polishing

- Defect etching

- Texturing

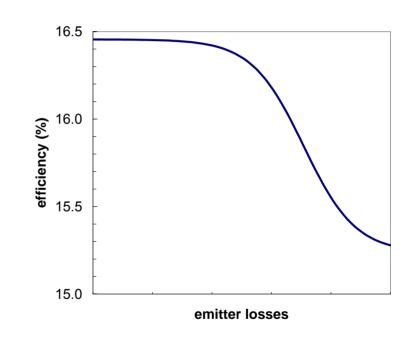

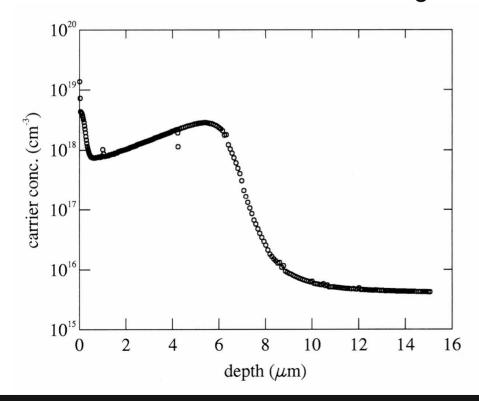

#### **Emitter processing**

Needed to form p-n junction

- Apply P source

- Diffusion at ~900 C for about 10 minutes

- Depth about 0.5 µm

- P concentration at surface: > 2×10<sup>20</sup> cm<sup>-3</sup>

- Higher concentration needed for good contacting

- However, it will result in additional recombination losses

Improved emitter/front side processing can give an efficiency gain of more than 0.5% absolute

#### **Emitter processing**

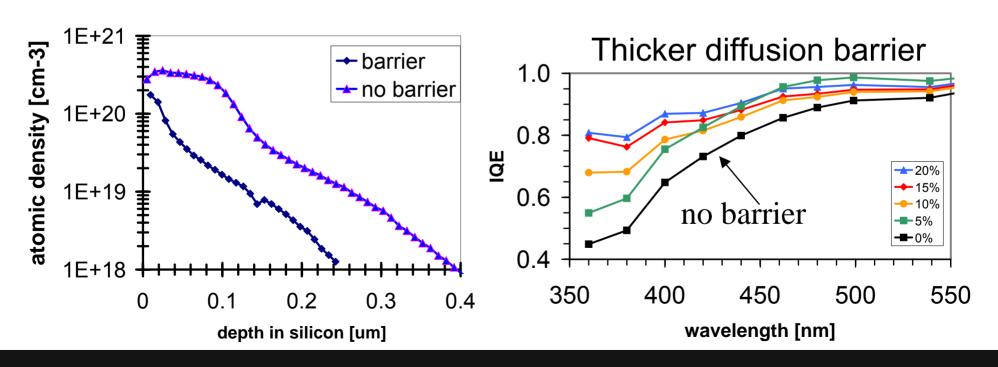

Effect dopant concentration on IQE

- Improved blue response (up to 550 nm) for lower dopant concentration

- Higher V<sub>oc</sub> and higher J<sub>sc</sub>: higher efficiency!

#### **Emitter processing**

Additional effect of emitter processing

- So-called gettering

- Diffusion of impurities to P rich layers (P-gettering)

- Impurities will not affect efficiency in those P rich layers

- Improved bulk quality and, thus, higher efficiency

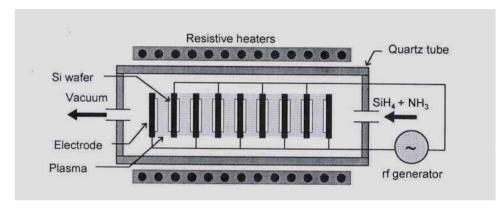

Applied using chemical vapour deposition

- Low pressure chemical vapour deposition (only surface passivation, ~700 C)

- Plasma enhanced chemical vapour deposition (different systems, ~400 C, 0.5-10 nm/s)

- Sputtering (several nm/s)

#### Functions SiN<sub>x</sub>:H layer

- Antireflection coating (70-80 nm)

- Surface passivation (reduced recombination at the surface)

- Bulk passivation (improved material quality)

- During anneal H diffuses into bulk and makes defects/impurities electrically inactive

Plasma Enhanced Chemical Vapour Deposition (PECVD)

- Parallel plate system

Direct plasma

- Wafers as electrodes

- Ion bombardment dependent on plasma frequency

- Damaged layer

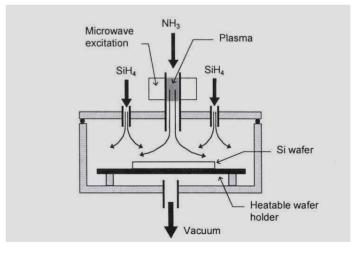

- Remote PECVD

- No ion bombardment

Aberle et al.

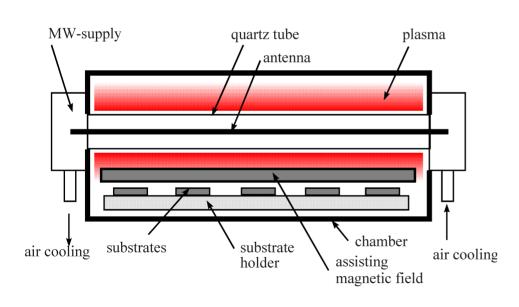

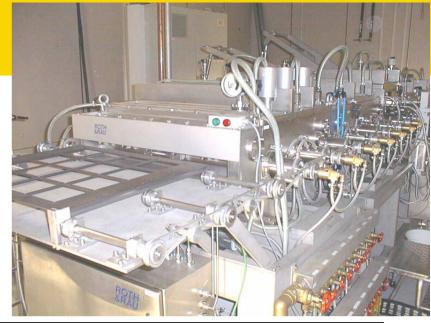

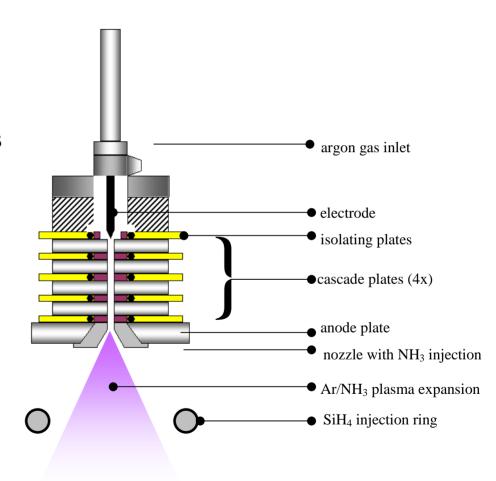

**ECN MicroWave Remote PECVD**

Deposition rate about 1 nm/s

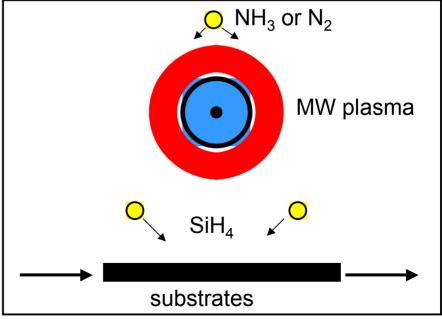

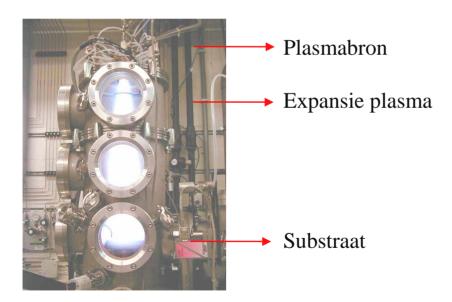

Expanding Thermal Plasma (ETP)

- Developed by TU/e

- Deposition rate 5-10 nm/s

- TU Delft: for thin film Si depositions

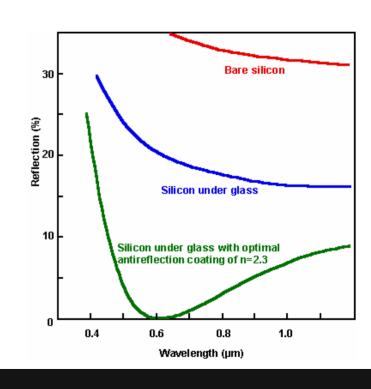

Optical specifications SiN<sub>x</sub>:H layer

Refractive index: n=2.1 higher n causes absorption at lower wavelength

SiN<sub>x</sub>:

$$n_1$$

;  $d_1$  Air:  $n_0$  ength Si:  $n_2$

$$n_1 = \sqrt{n_0 n_2} \qquad d_1 = \frac{\lambda_0}{4 n_1}$$

- Ideal for air-Si: *n*=1.9; d=~80 nm

- Ideal for air-glass-Si: n=2.3; d=~65 nm (absorption SiN<sub>x</sub> too high)

- n can be tuned with gas composition

- Higher n: more Si (SiH<sub>4</sub>)

- Lower n: more N (NH<sub>3</sub>)

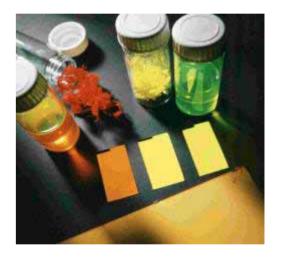

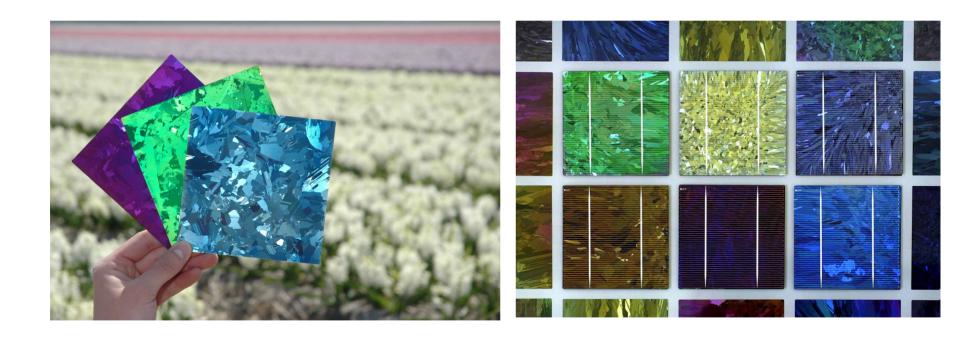

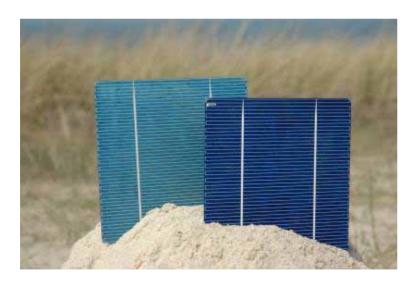

Optical specifications SiN<sub>x</sub>:H layer

• Different layer thickness: different colour

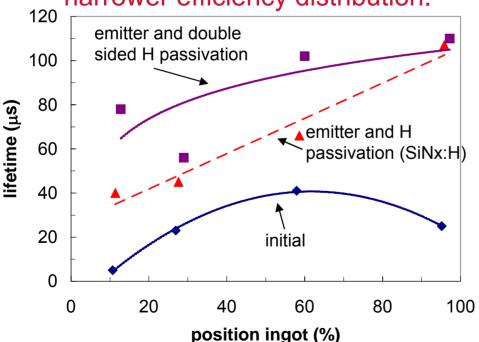

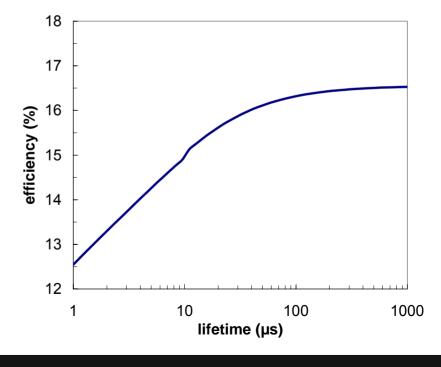

## Gettering and bulk passivation (emitter and SiN<sub>x</sub>:H)

Improved bulk quality using gettering and passivation

Lifetime>100 µs will hardly affect cell efficiency (diffusion length 2 times cell thickness)

Besides higher efficiency, gettering and passivation will result in a

narrower efficiency distribution.

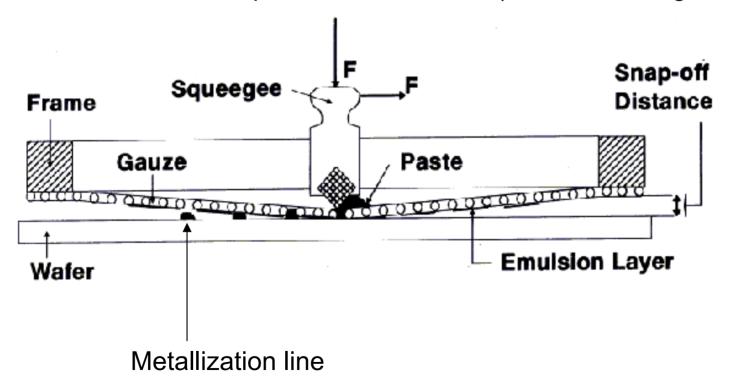

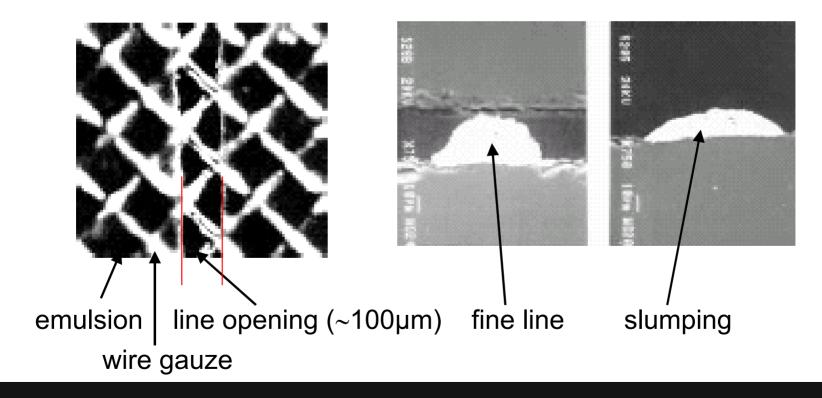

Screen-printing process and sintering in belt furnace

Principle screen-printing process

- Metallization paste is 'pressed' through pattern in screen

- Paste contains metal particles and oxides (etches Si at higher T)

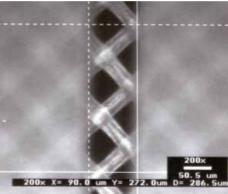

Ag front side metallization

• Fine line metallization printed through patterned screen

Fine line printing

- Reduced shading losses

- Contact resistance might be critical

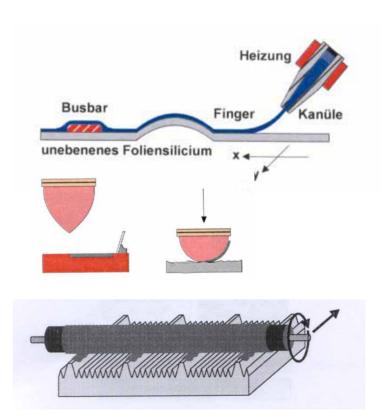

- Other techniques:

- Plating (electroless)

- Dispensing

Pad printing

Roller printing

Al rear side (Back Surface Field to reduce recombination at surface)

- After sintering step (around 800 C, few seconds) highly doped layer

- Better BSF when thicker and higher doped

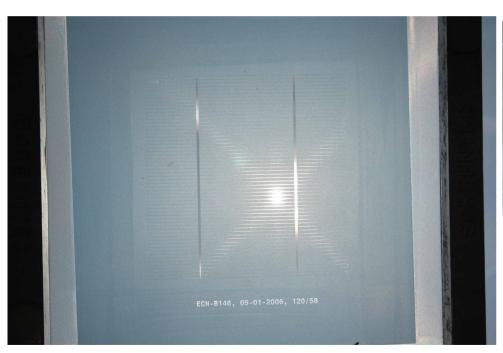

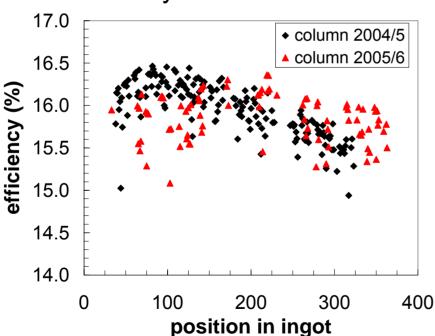

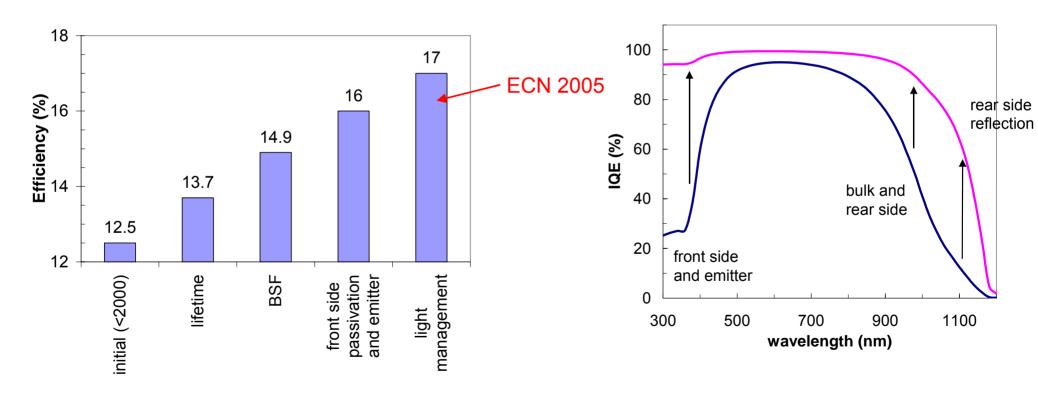

## **Efficiency ECN process**

#### **Results ECN Baseline process**

Processing two complete columns (different ingots) of wafers during 2 years

- Average 16.0%

- In industry about 15%

Wafer size: 125x125 mm<sup>2</sup>

Thickness: ~300 µm

Material: p-type mc-Si

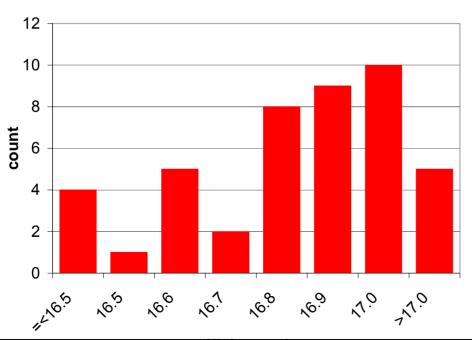

## **Efficiency ECN process**

- High-efficiency (17%) in-line process (300 µm thick; 156 cm² mc-Si)

- 50 cells processed (best efficiency 17.1%; average 16.8%)

- Module made using cover glass with ARC Full area efficiency 14.8%; encapsulated cell eff: 16.8%

V<sub>OC</sub>=22.2 V; I<sub>SC</sub>=5.76A; FF=0.738; P=94.3 Wp

#### **Efficiency ECN process**

• From 2000 up to now

#### **Future improvements**

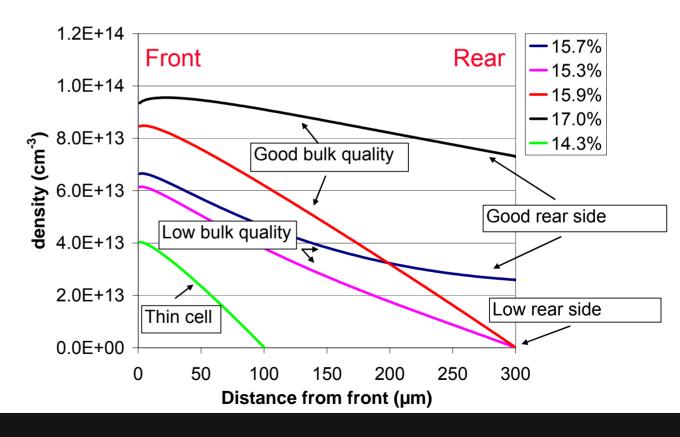

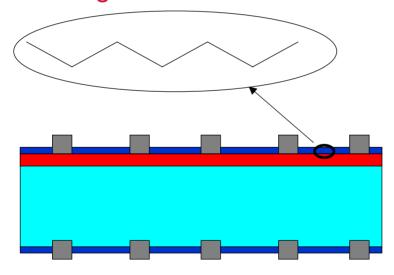

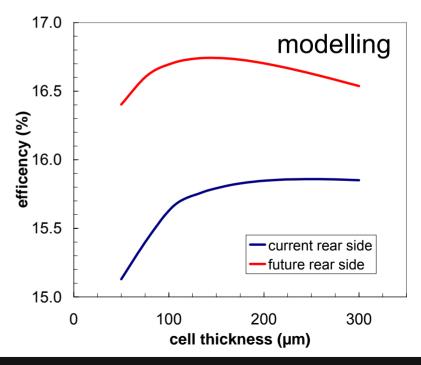

#### Thin wafers

Rear side critical

# Minority carrier density

Combination of generation and recombination

17.0%: good bulk and rear 15.9%: good bulk, low rear 15.7%: low bulk, good rear 15.3%: low bulk and rear 14.3%: as 15.9%, but thin

#### **Future improvement**

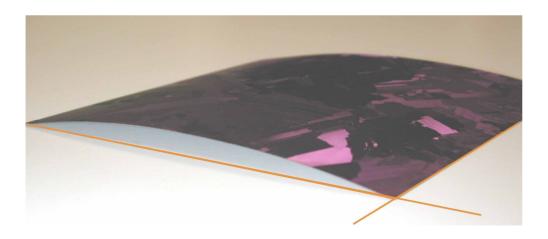

Al rear side (Back Surface Field to reduce recombination at surface)

17% reached on 300 µm thick wafers

#### However:

- Bowing for thinner wafers

- Recombination losses too high for high efficiencies (>18%)

- Internal reflection too low (~70%) for high efficiencies

#### Future improvements rear side

#### Thin wafers

- Rear side critical (bowing, reflection, BSF)

- New rear side processing using for example SiN<sub>x</sub>

- Higher efficiencies for thinner wafers

SiN<sub>x</sub> for rear side passivation Local rear contacts / BSF

#### Future improvements rear side

#### Thin wafers

- New rear side processing using SiN<sub>x</sub>

- 16.4% obtained by ECN with baseline-like processing

- About 1% absolute higher than reference with AI BSF (obtained efficiency depends on Si material quality)

### **Future improvements**

Thin wafers (less dependent on material quality)

- Improved light management

- Texturing

- Light trapping

- Improved emitter (reduce losses)

- Perfect surface passivation

- Both surfaces

- Less metallization losses

- Series resistance (contact and line resistance)

- Reduced shading losses

20% mc-Si cell efficiency should be possible! (long term)

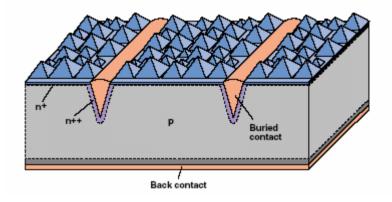

### Other industrial cell concepts

Laser Grooved Buried Contacts

BP Solar

Monocrystalline

Rear side contacted cell

SunPower

- ~20%!

- High quality and expensive material

## Other industrial cell concepts

#### SunPower

- Cell 21.8%

- n-type material

- Module: full area 18.1%

#### Sanyo

- HIT cell: 21.8%

- n-type material

- Emitter deposited

#### **Record efficiencies**

Monocrystalline (4 cm<sup>2</sup>): 24.7%

Monocrystalline (149 cm<sup>2</sup>): 21.5%

Multicrystalline (1 cm<sup>2</sup>): 20.3%

Multicrystalline (137 cm<sup>2</sup>): 18.1%

ECN multi (156 cm<sup>2</sup>): 17.0%

Single layer ARC; homogeneous emitter; inline processing

Highest efficiency with completely inline processing

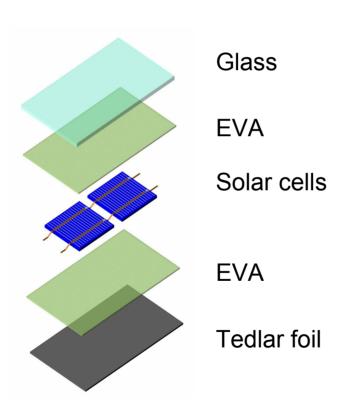

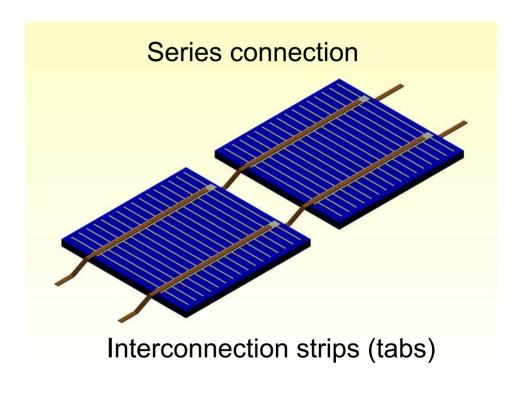

Conventional module technology (soldering)

### Conventional module technology

interconnection

lamination

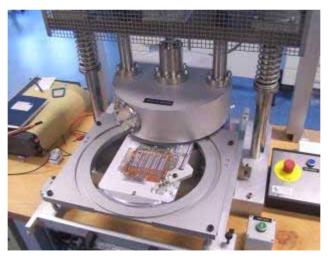

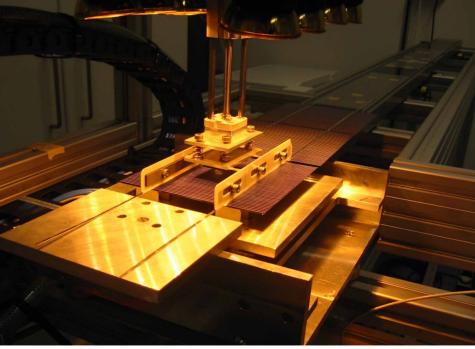

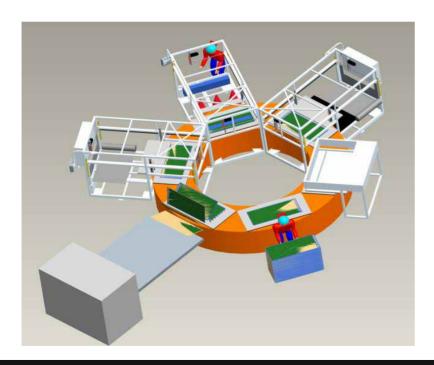

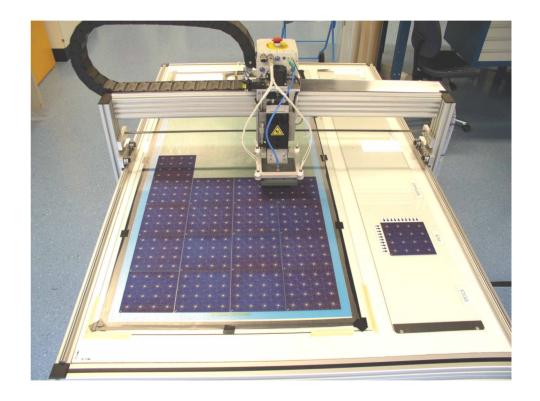

Pilot-line tabber-stringer for interconnection

Pilot line to be built at ECN

Fully automated and realibility-tested interconnection process for back-contact cells and suitable for thin and fragile cells

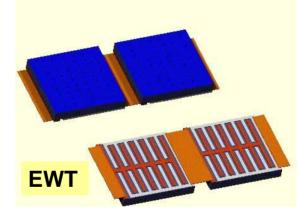

New module technology:

- New cell designs needed

- Back contacted

- Simple interconnection

- Can be used for thin cells

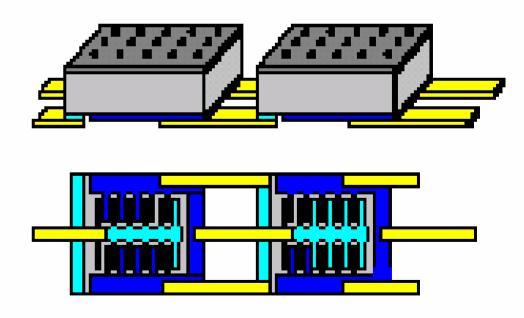

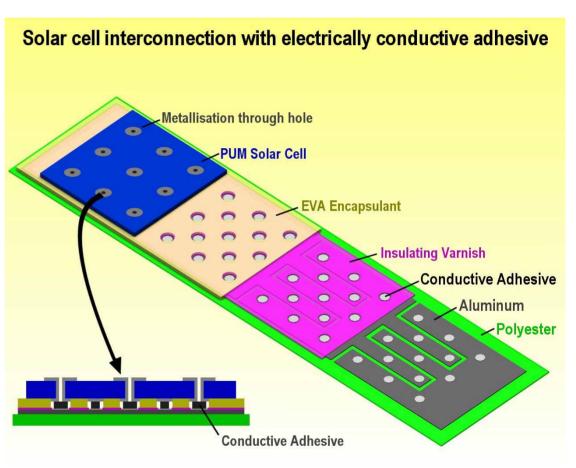

**MWT**

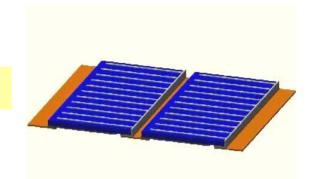

### **Emitter Wrap Through:**

- No metallization on the front

- Thousands of holes

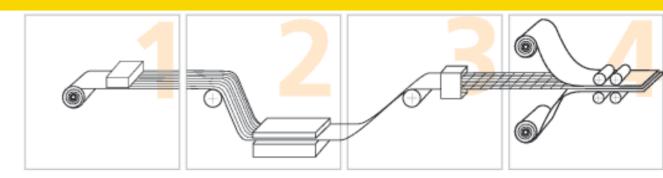

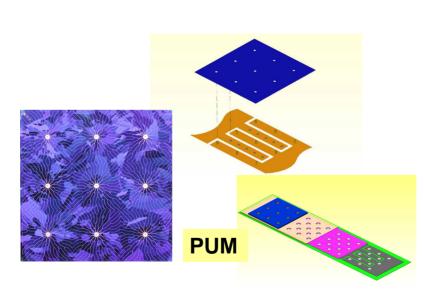

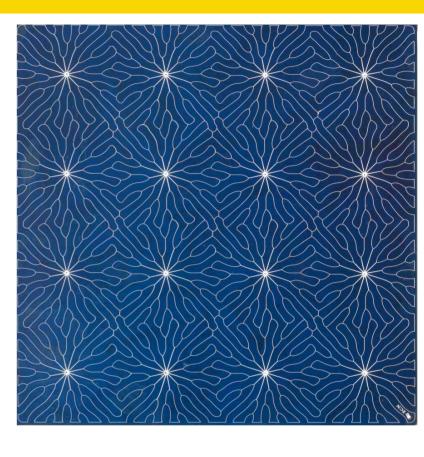

#### ECN's PUM concept:

- More energy from attractive cells

- 2-3% less shading

- Resistance losses independent on cell size (only on size unit cell)

- Standard cell processing except:

- Laser drilling holes

- Junction isolation around holes

Mother Nature's water lily

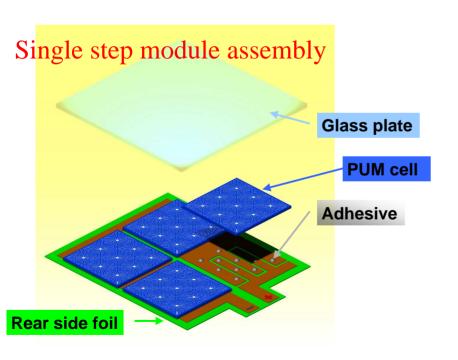

#### ECN's PUM concept:

Single shot interconnection and encapsulation

#### ECN's PUM process:

- Foil preparation

- Apply conductive adhesive instead of soldering (lower stress)

- Pick and place cells

- One step curing and encapsulation

#### ECN's PUM result:

- Full size module (71×147 cm<sup>2</sup>)

- 128 Wp (15.8% encapsulated cell efficiency)

- 0.6-0.8% absolute efficiency gain

#### Best PUM cell result up to now:

• 16.7% (225 cm<sup>2</sup>)

At this moment PUM is the only integrated concept for cell and module

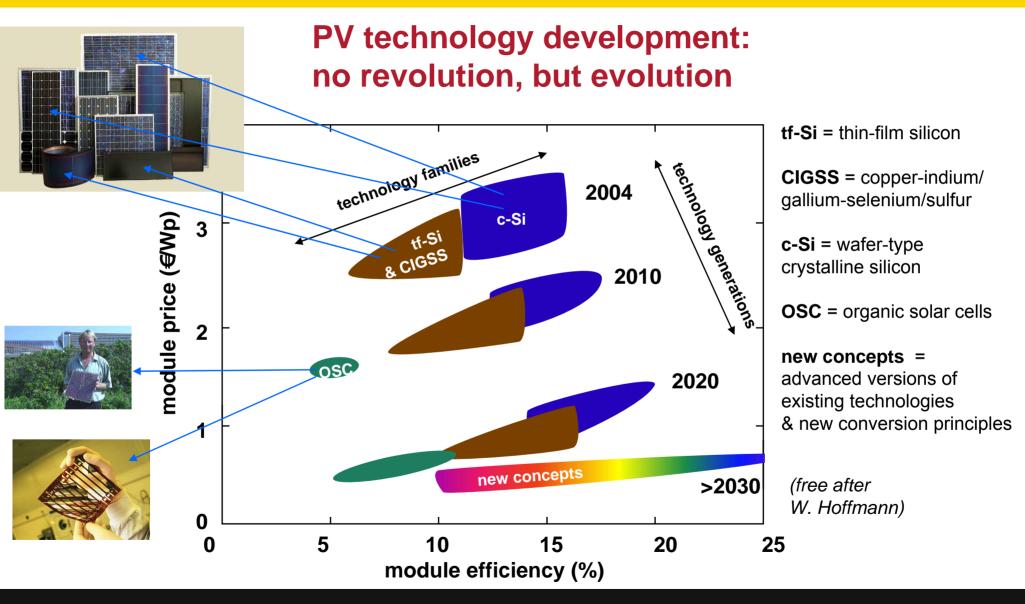

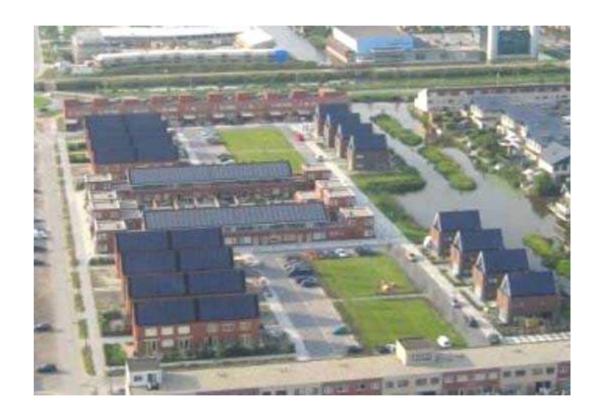

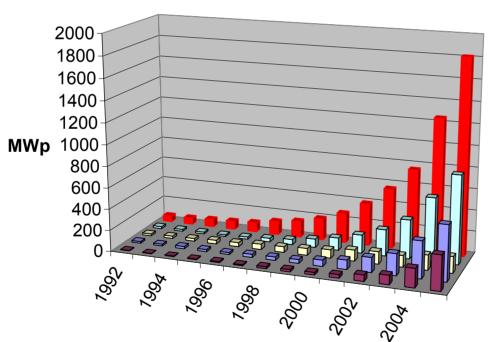

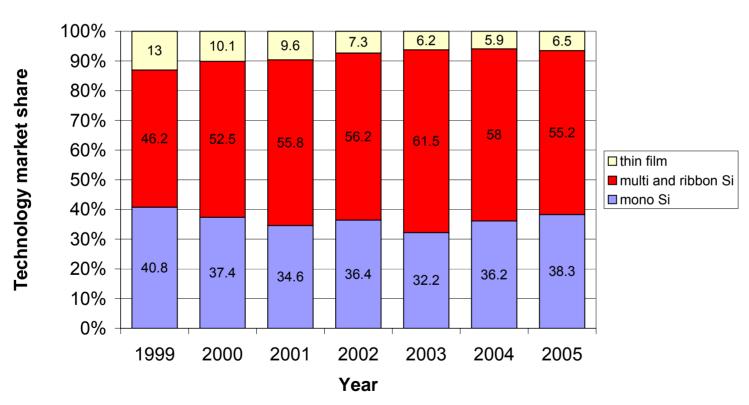

#### **PV** market

Annual market growth more than 40%

Growth rate 2004: 67%

2005: 1720 MWp (+44%)

Japan: ~50% market share

Photon International, 2006

### **PV** market

More than 90% crystalline Si technology

Photon International, 2006

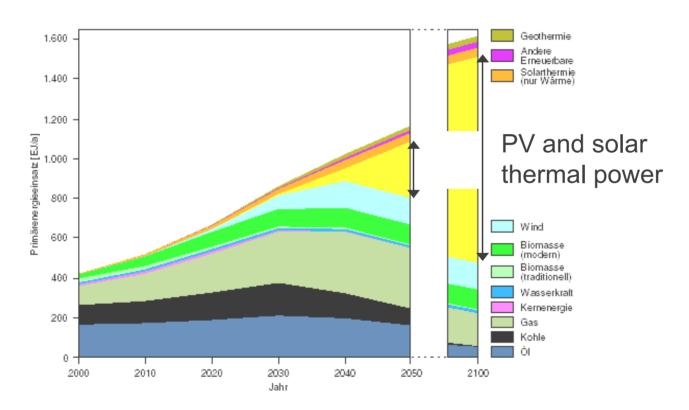

#### **PV** market

Expected market: solar the most important primary energy source

Wissenschaftliche Beirat 2003

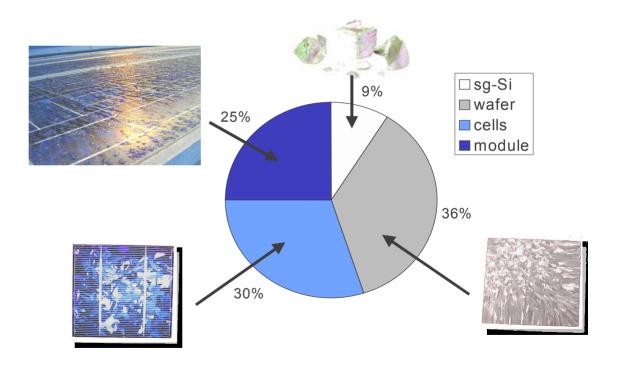

#### **Costs PV**

Contributes wafer is about 45%!

Thinner wafers, or better ribbons, important!

Price solar electricity:

0.20-0.50 €/kWh (depending on location)

NL: ~0.50 €/kWh

- Less material use

- Thin ribbons

- Less module materials

- High efficiencies for the same process costs

- Advanced processing

- New cell design

- Easy manufacturing

- Automation

- Easy module manufacturing

- High lifetime

- Improved yearly system output

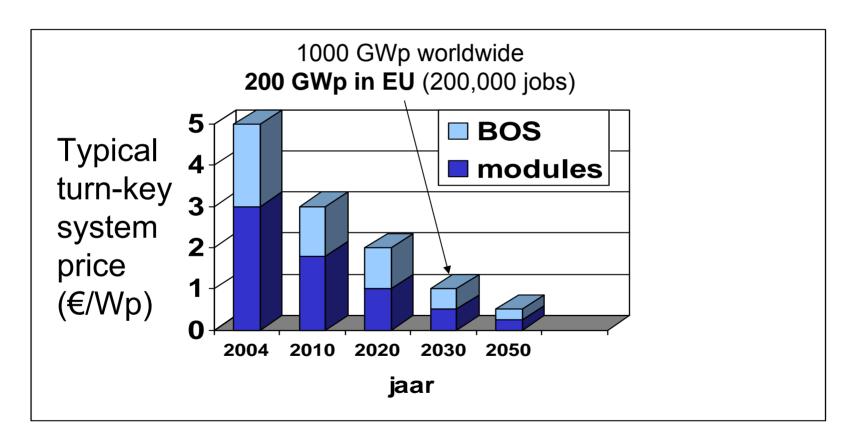

Expected costs

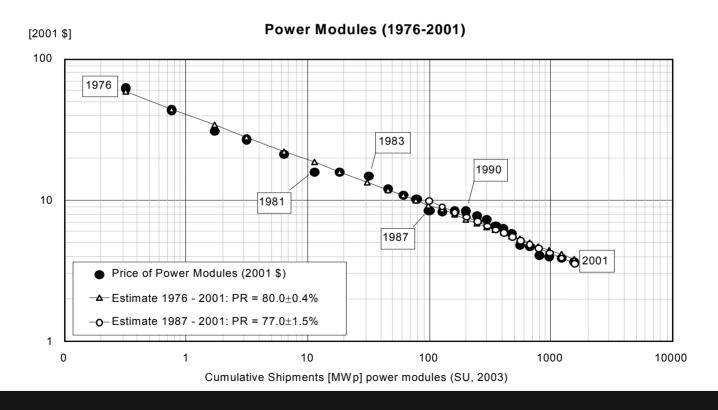

- Expected costs based on learning curves (EU project Photex)

- Combined effect of technology development, experience, ....

- Progress ratio PR should be around 80%

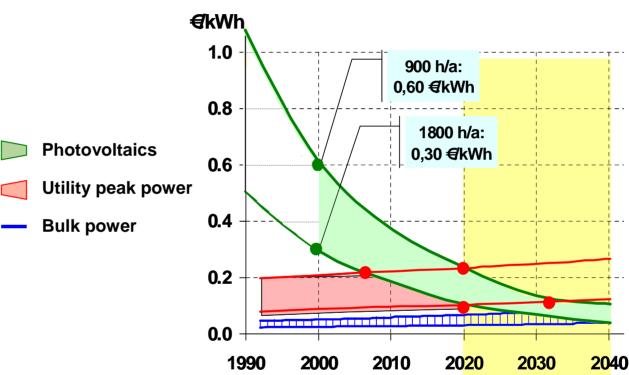

Expected costs

Solar competitive between 2010-2020

Source: RWE Energie AG and RSS GmbH

Towards an Effective European Industrial Policy for PV.ppt / 05.06.2004 / Rapp

@ RWE SCHOTT Solar GmbH

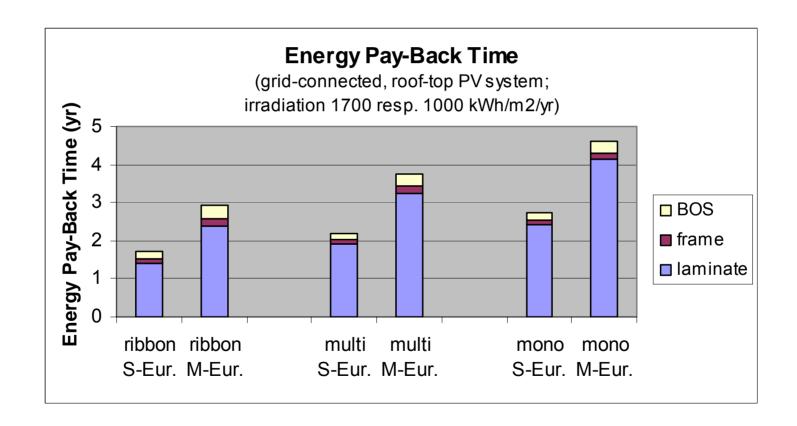

### **Environmental aspects**

Energy Pay Back Time 2005

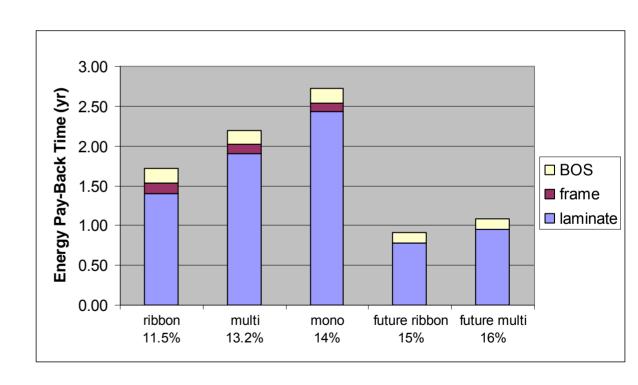

### **Environmental aspects**

Energy Pay Back Time 2005 and 2010<sup>+</sup>

- Low energy consumption especially for Solar Grade Si

- Low material use (abundance)

- High efficiency

- High lifetime modules

- Environmental friendly processes

- Recycling

#### **Conclusions**

- Solar Grade Silicon needed for growing market

- Effect of impurities on cell efficiency should be known

- Less Si use with ribbons

- Improved processing has led to 17% mc-Si efficiency using in-line processing

- New processes for thin wafers/ribbons under development

- Integrated cell and module design like PUM needed

- High module lifetime

#### Then

- Cost reduction possible

- Will be competitive with bulk electricity price

- Energy Pay Back Time can be reduced to <1 year</li>

- Solar energy will be the most important primary energy source in 2100

# **Applications at ECN**

# **Applications**